Design Examples¶

In this course, digital design concepts and SystemVerilog features will be introduced through examples of gradually increasing complexity, inspired by real digital systems, as follows:

# |

Design |

File List |

RTL |

TB |

Sim & GDS |

|---|---|---|---|---|---|

1 |

Not Gate |

||||

2 |

Full Adder |

||||

3 |

N-Adder |

||||

4 |

ALU |

||||

5 |

Encoder |

— |

— |

— |

— |

6 |

Decoder |

— |

— |

— |

— |

7 |

Verilog Functions |

— |

— |

— |

— |

8 |

Flip Flop |

||||

9 |

Up counter |

||||

10 |

Binary Reduction Tree to find minimum of a vector |

||||

11 |

Parallel to Serial Converter |

||||

12 |

Down counter |

||||

13 |

UART RX |

||||

14 |

UART TX |

||||

15 |

UART Echo (RX + TX) |

||||

16 |

FIR Filter Retimed RTL |

||||

17 |

UART RX + TX + FIR Filter |

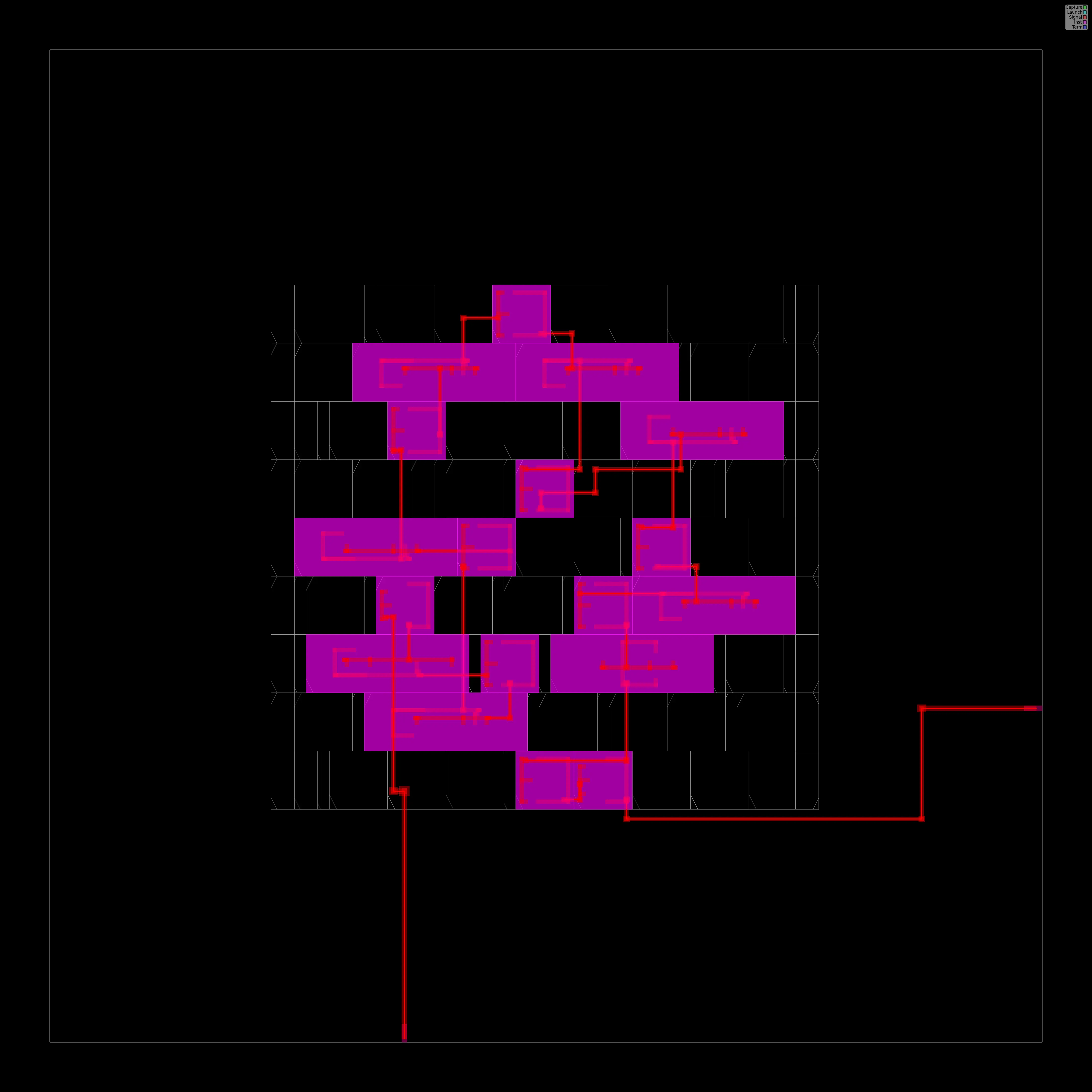

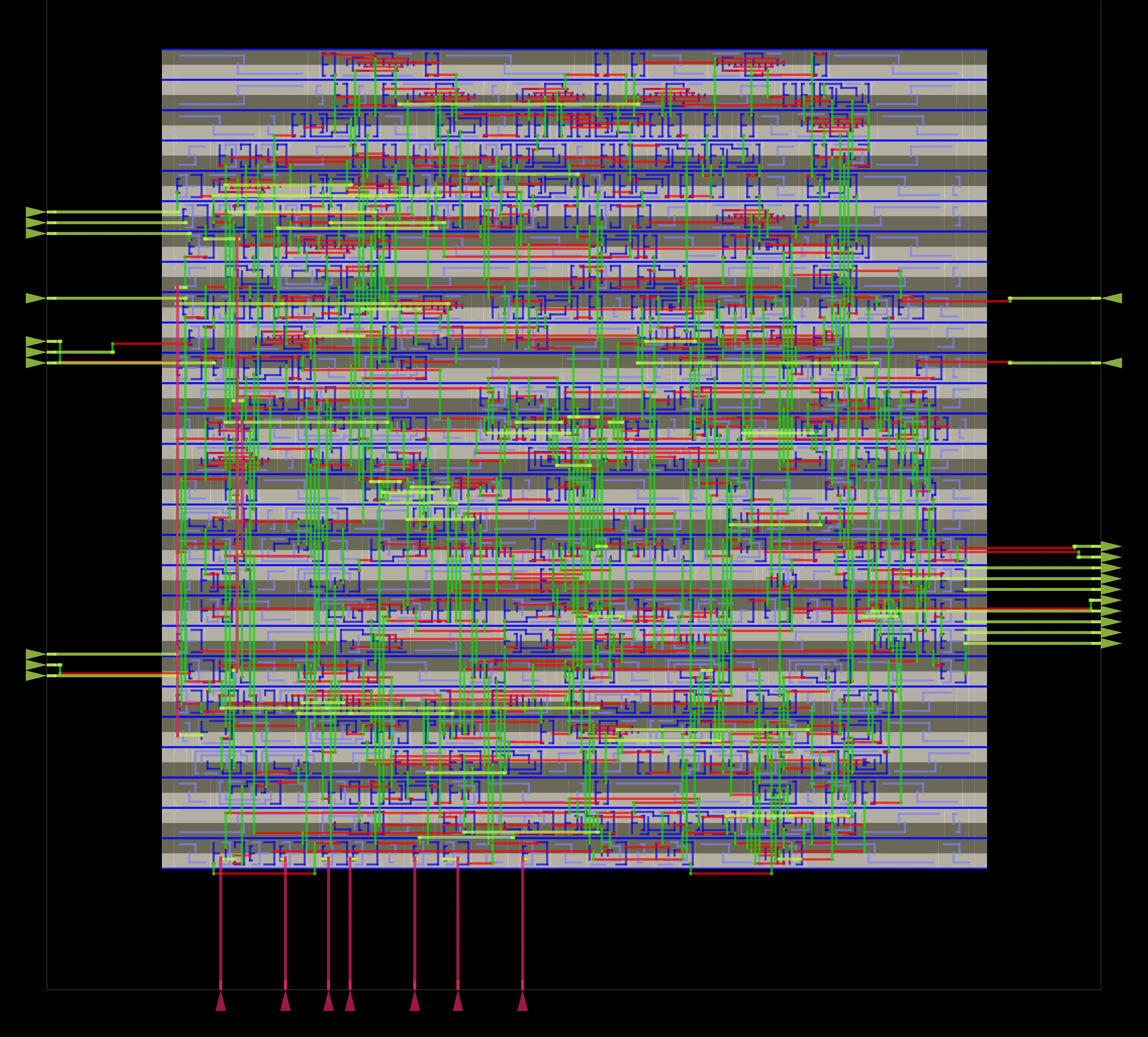

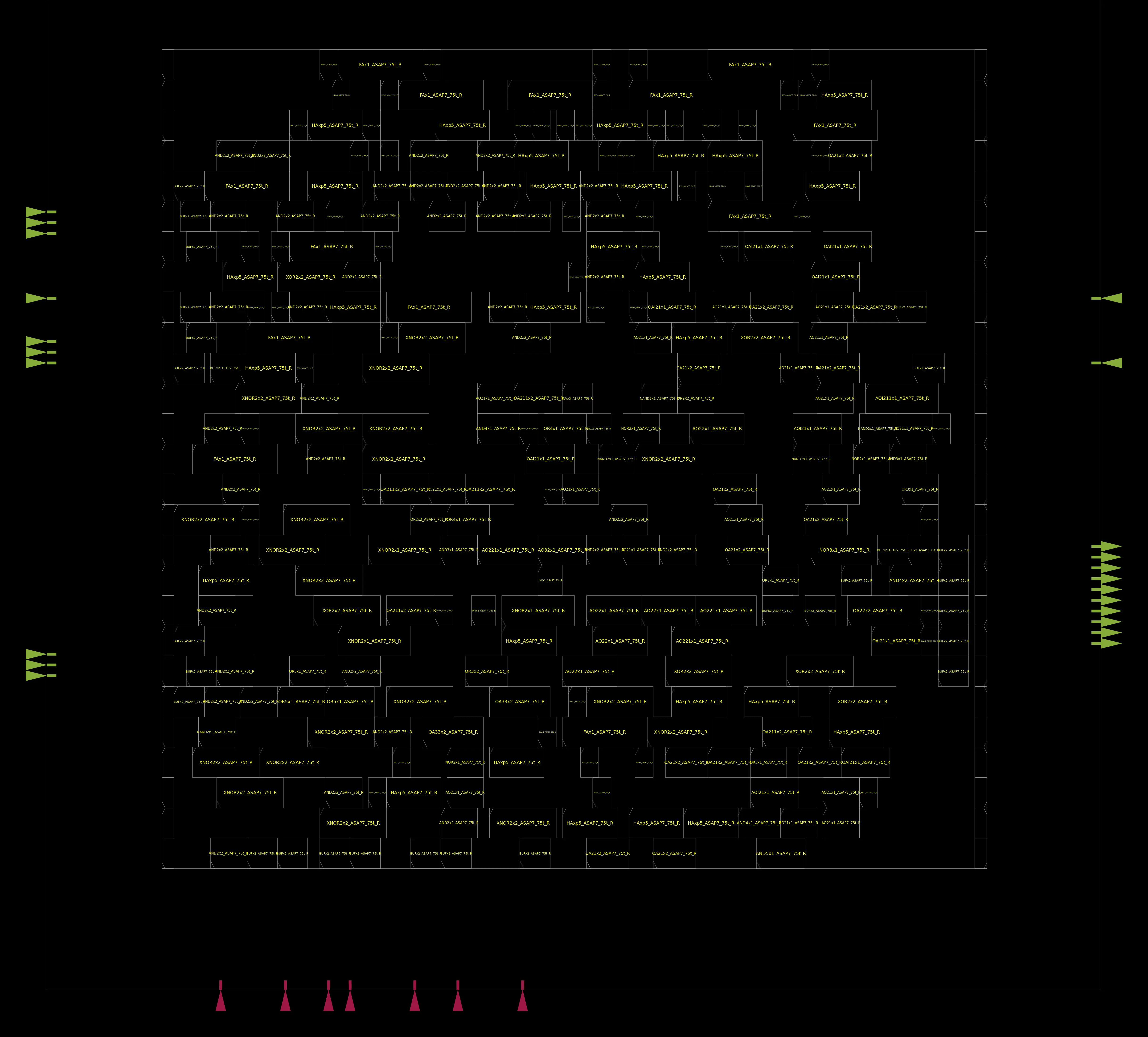

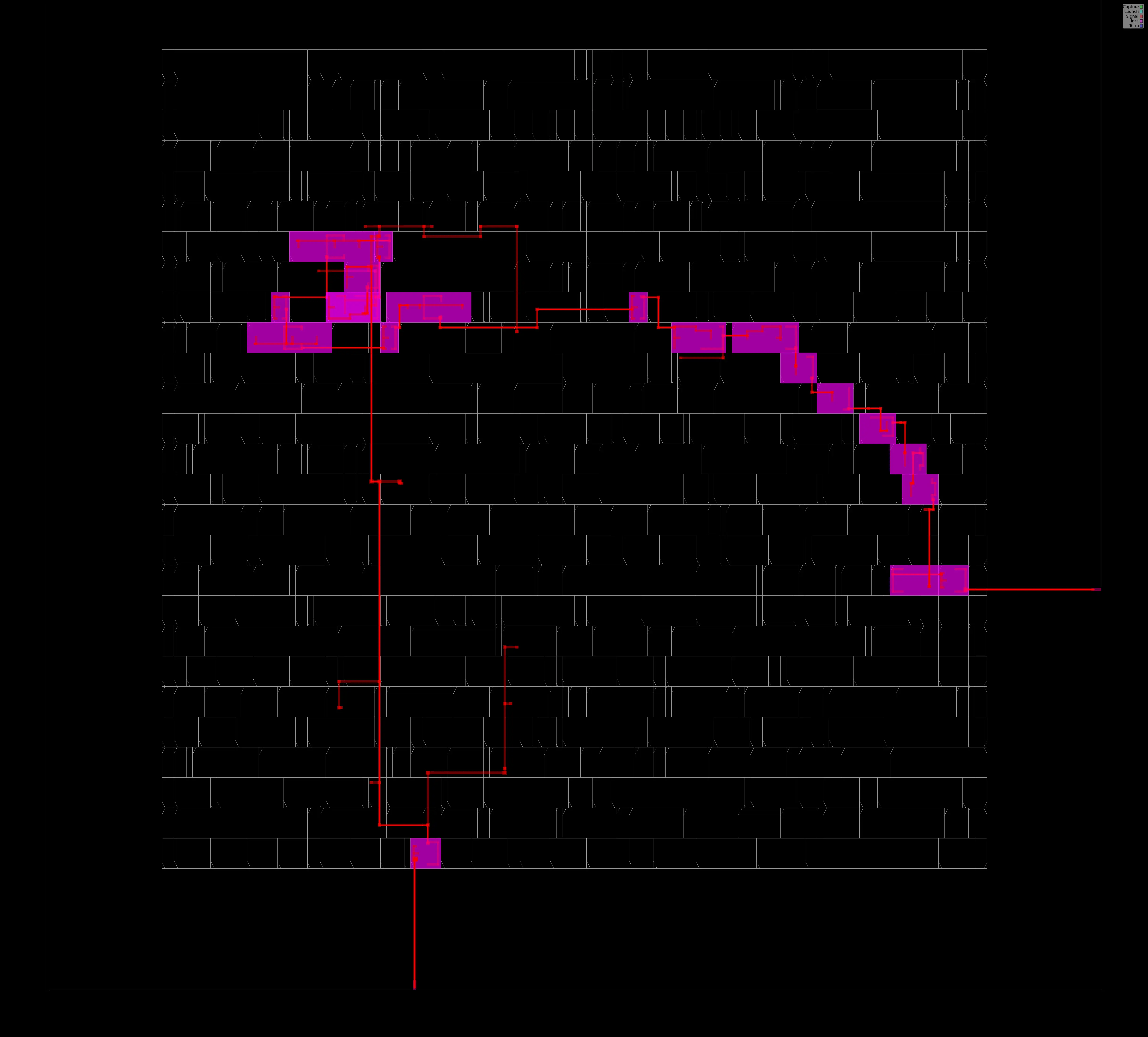

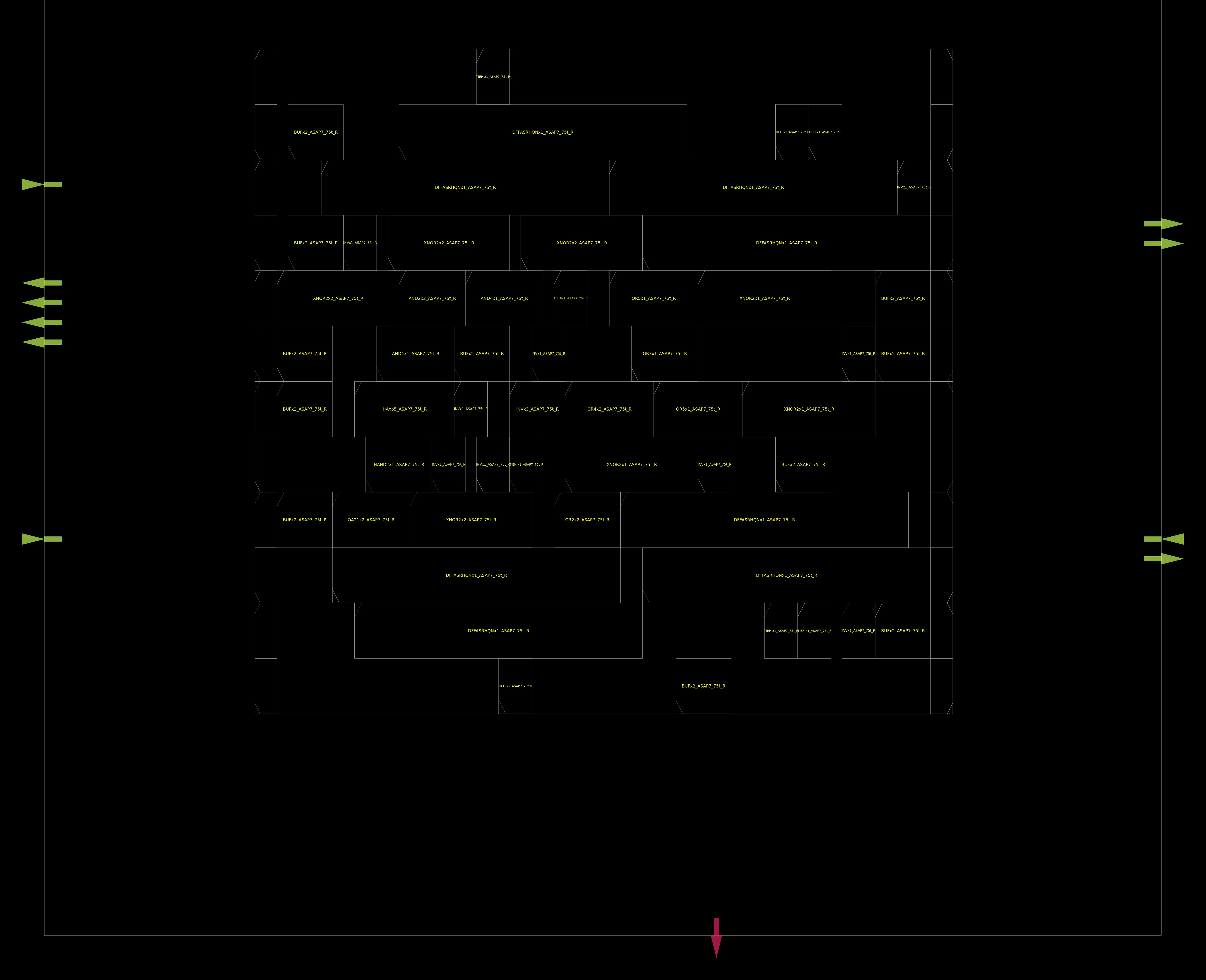

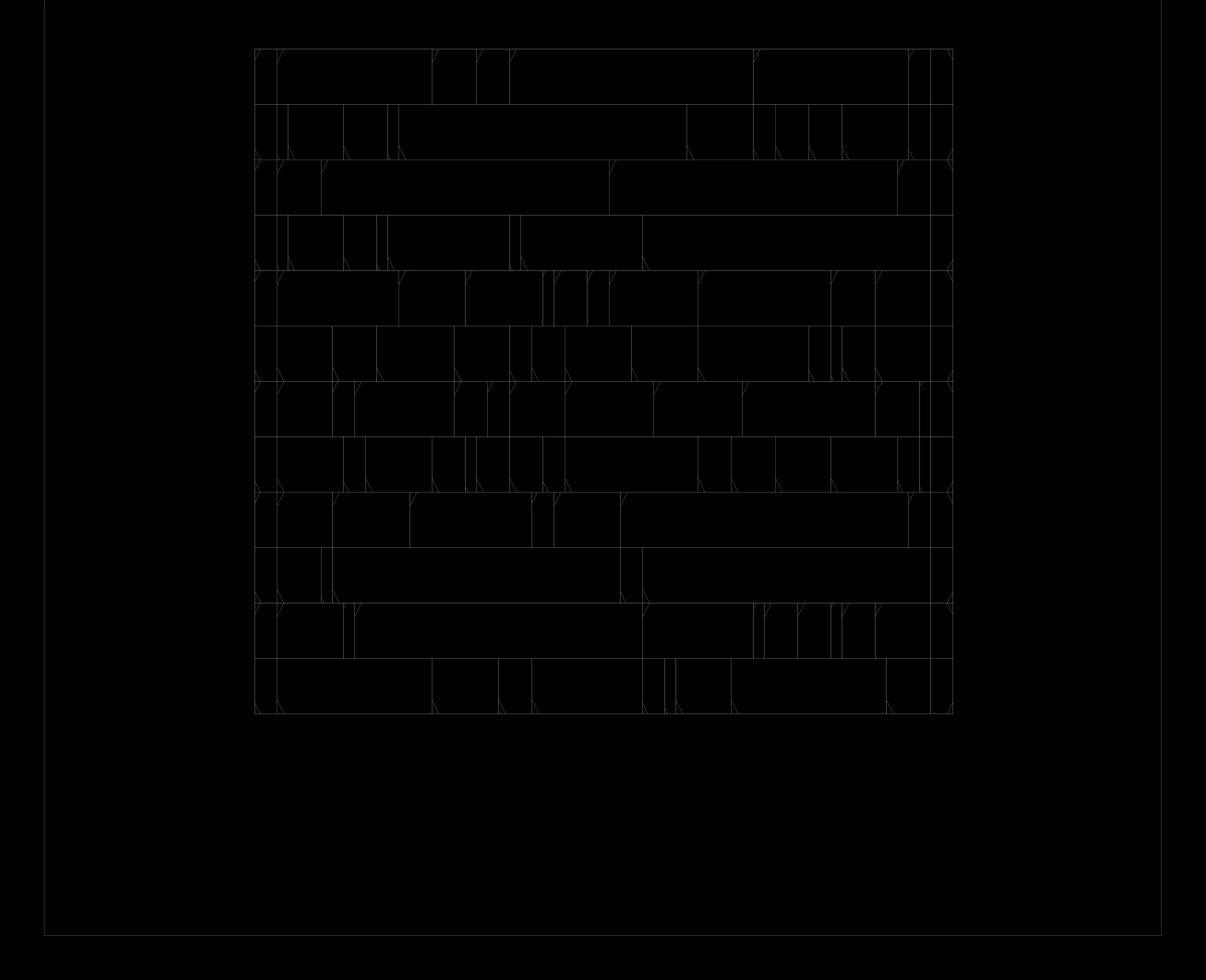

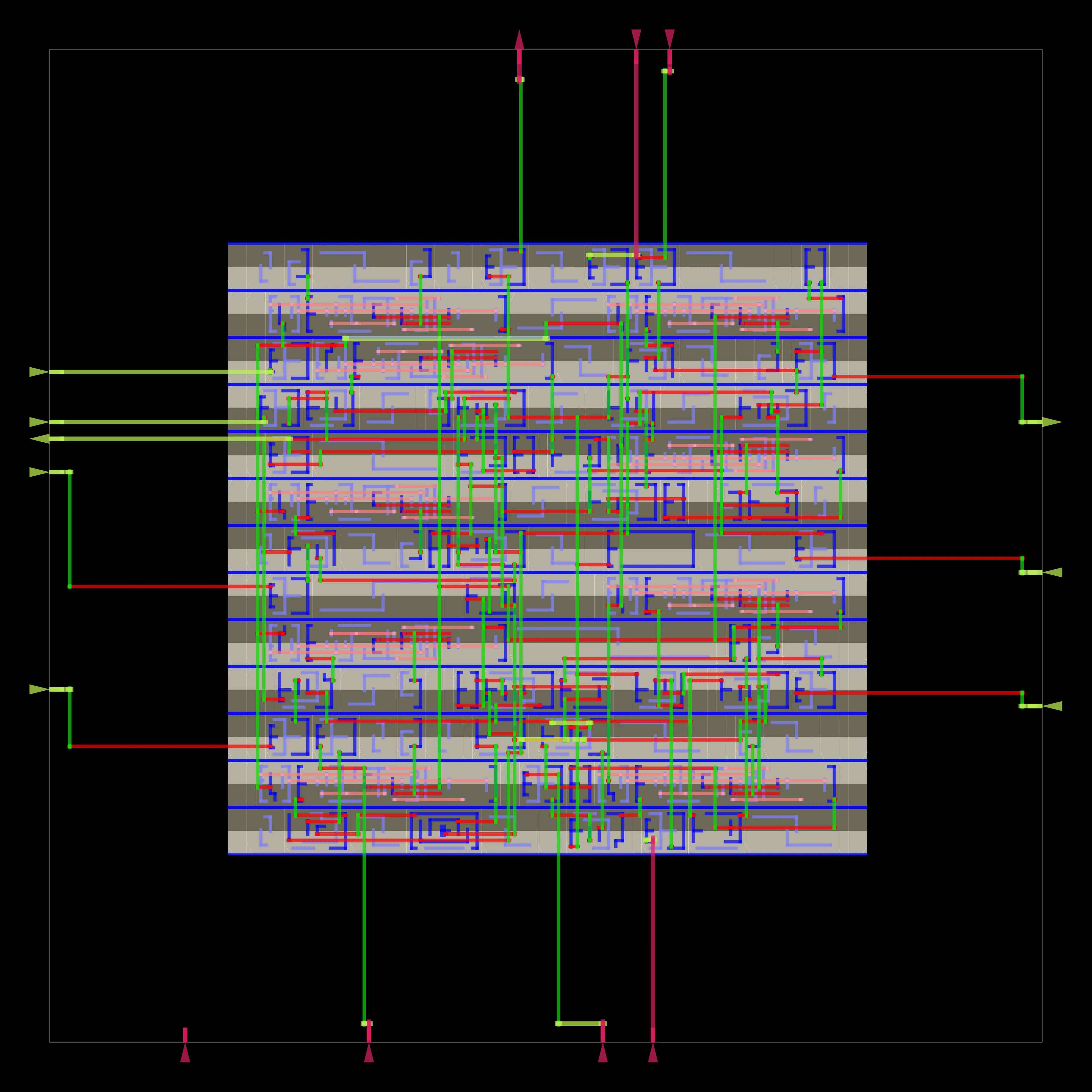

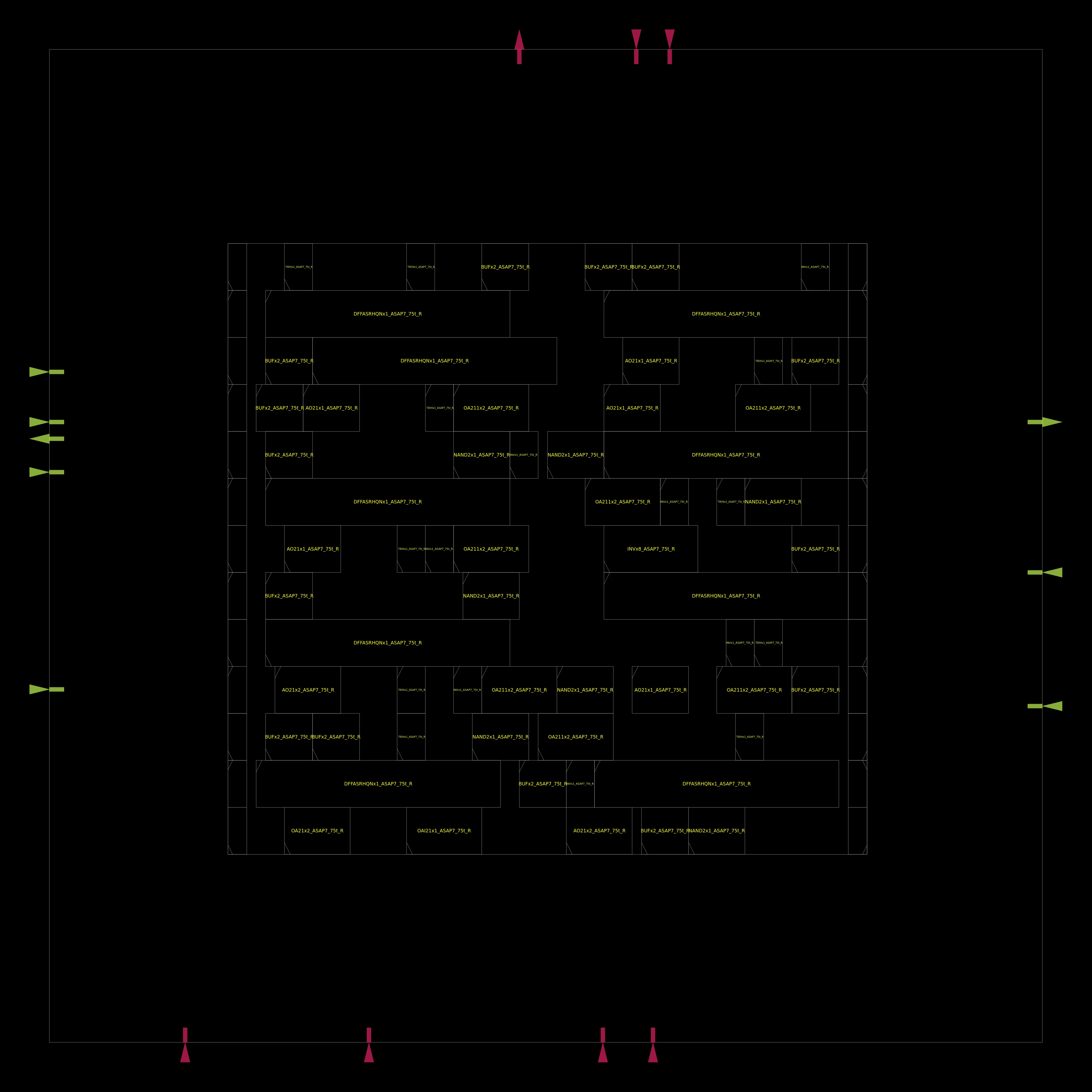

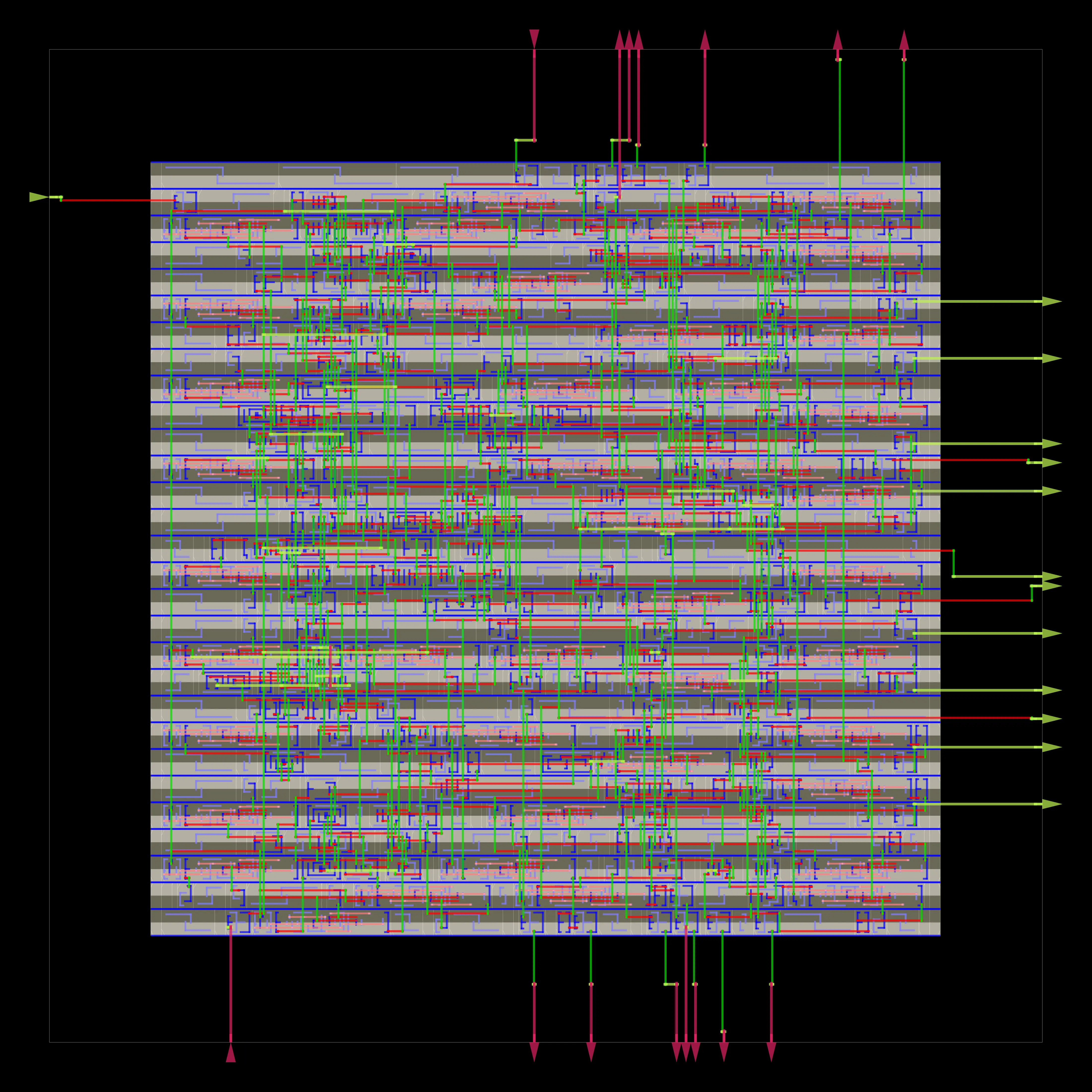

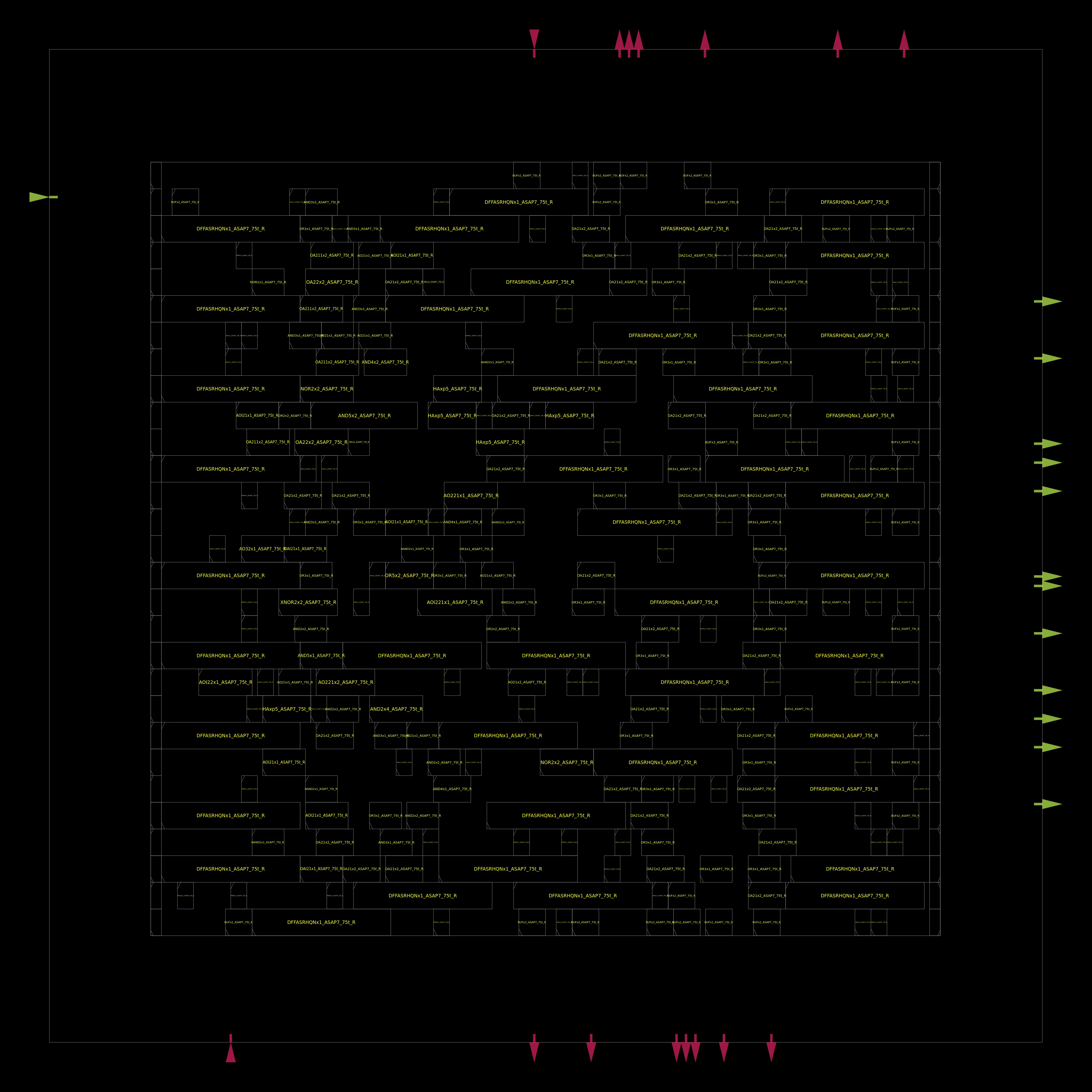

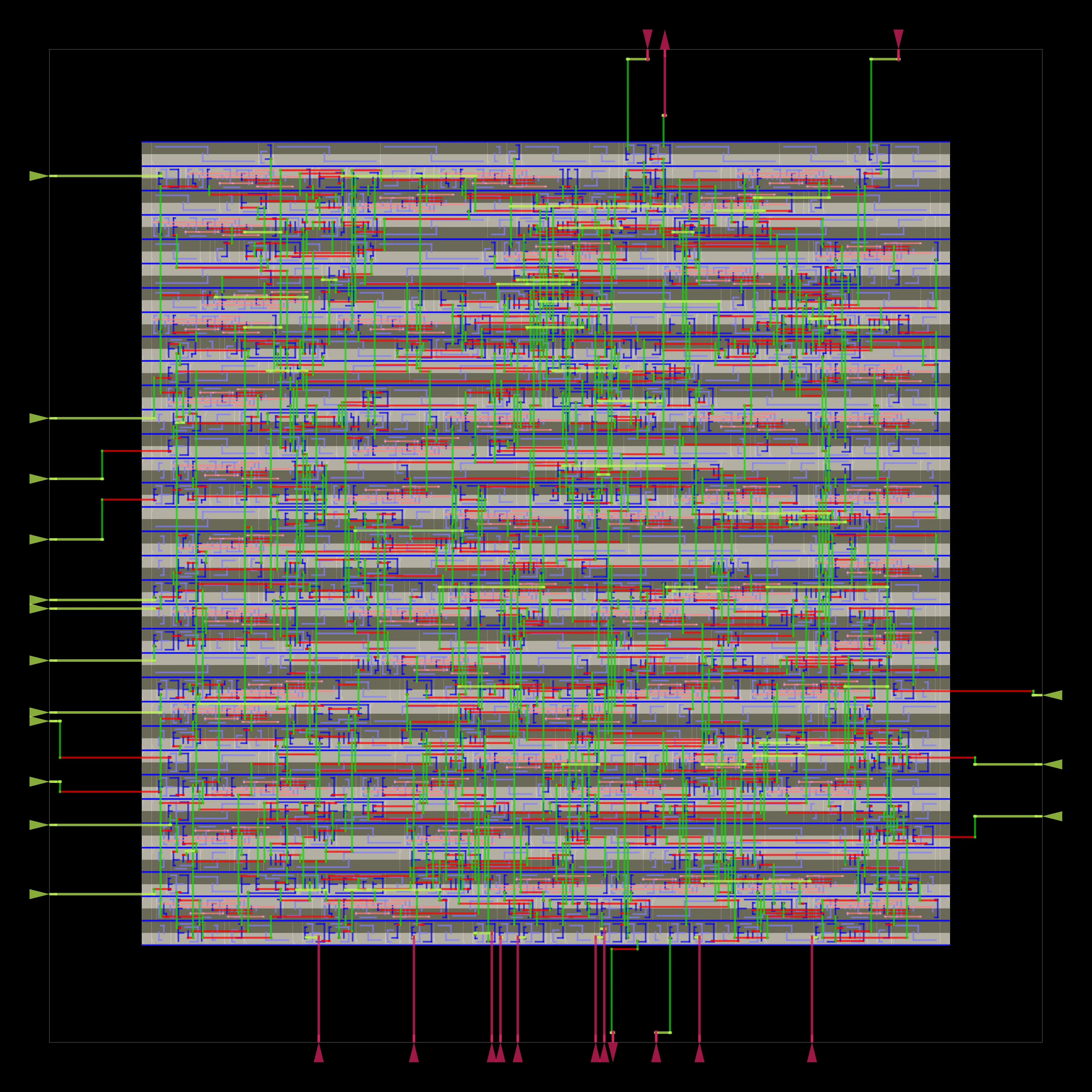

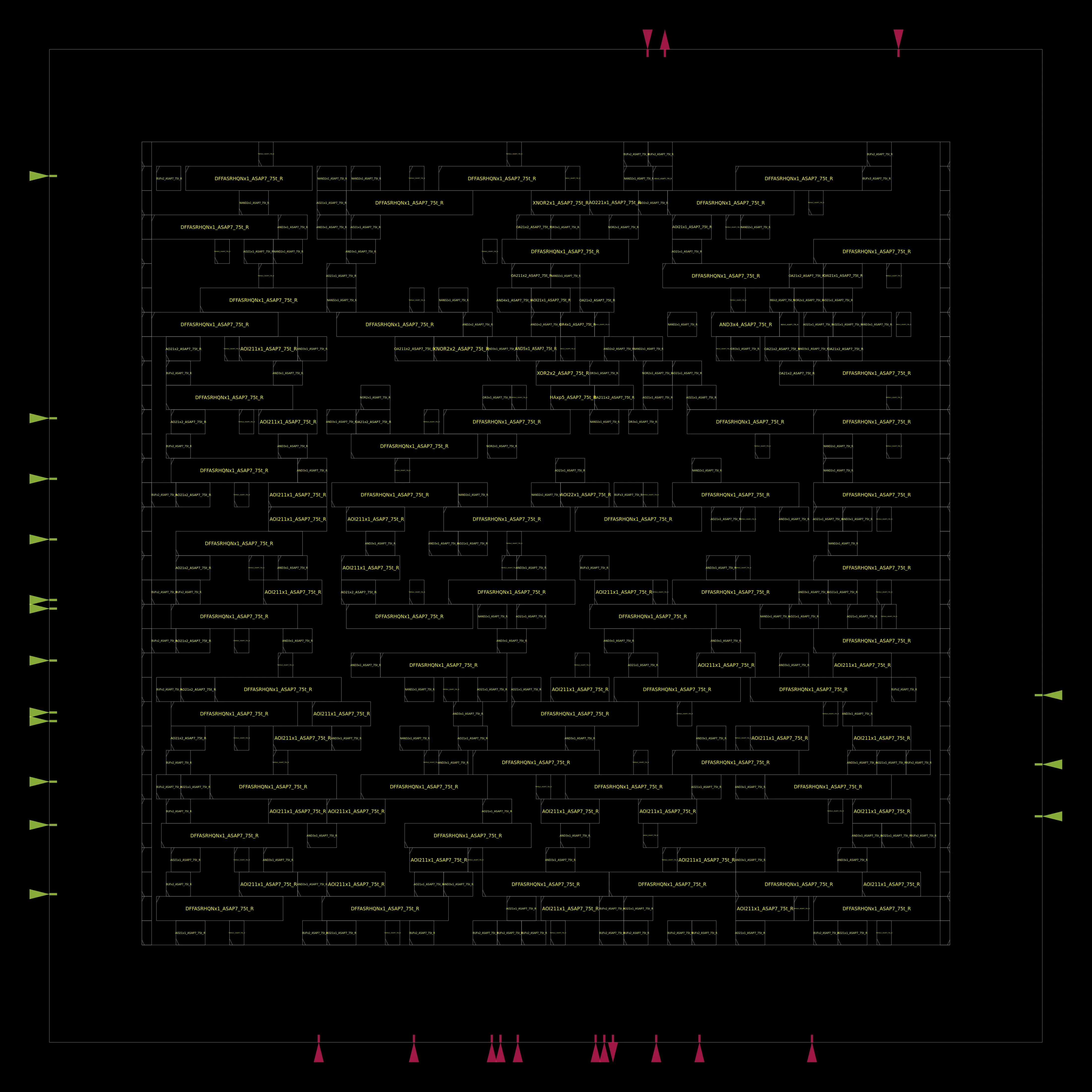

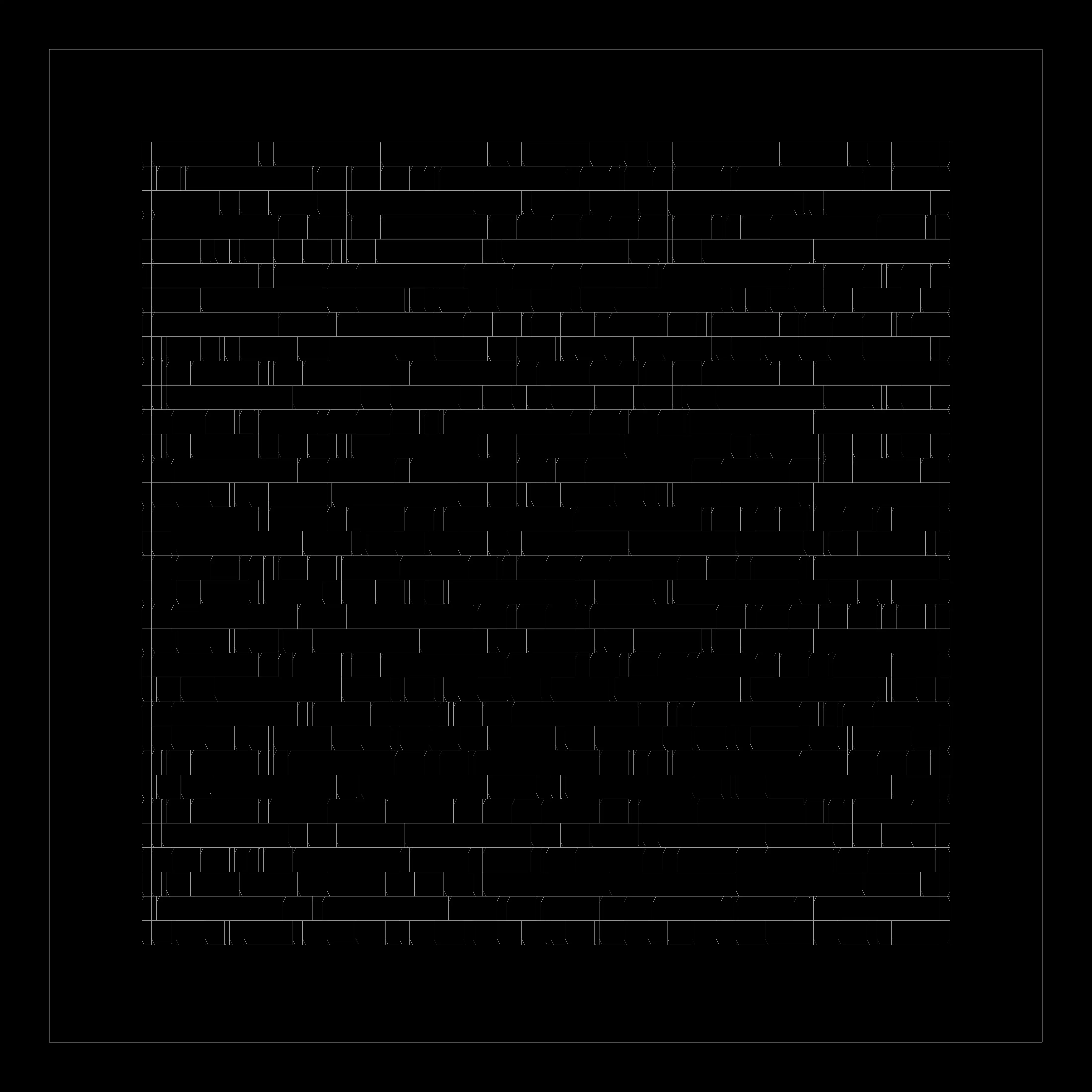

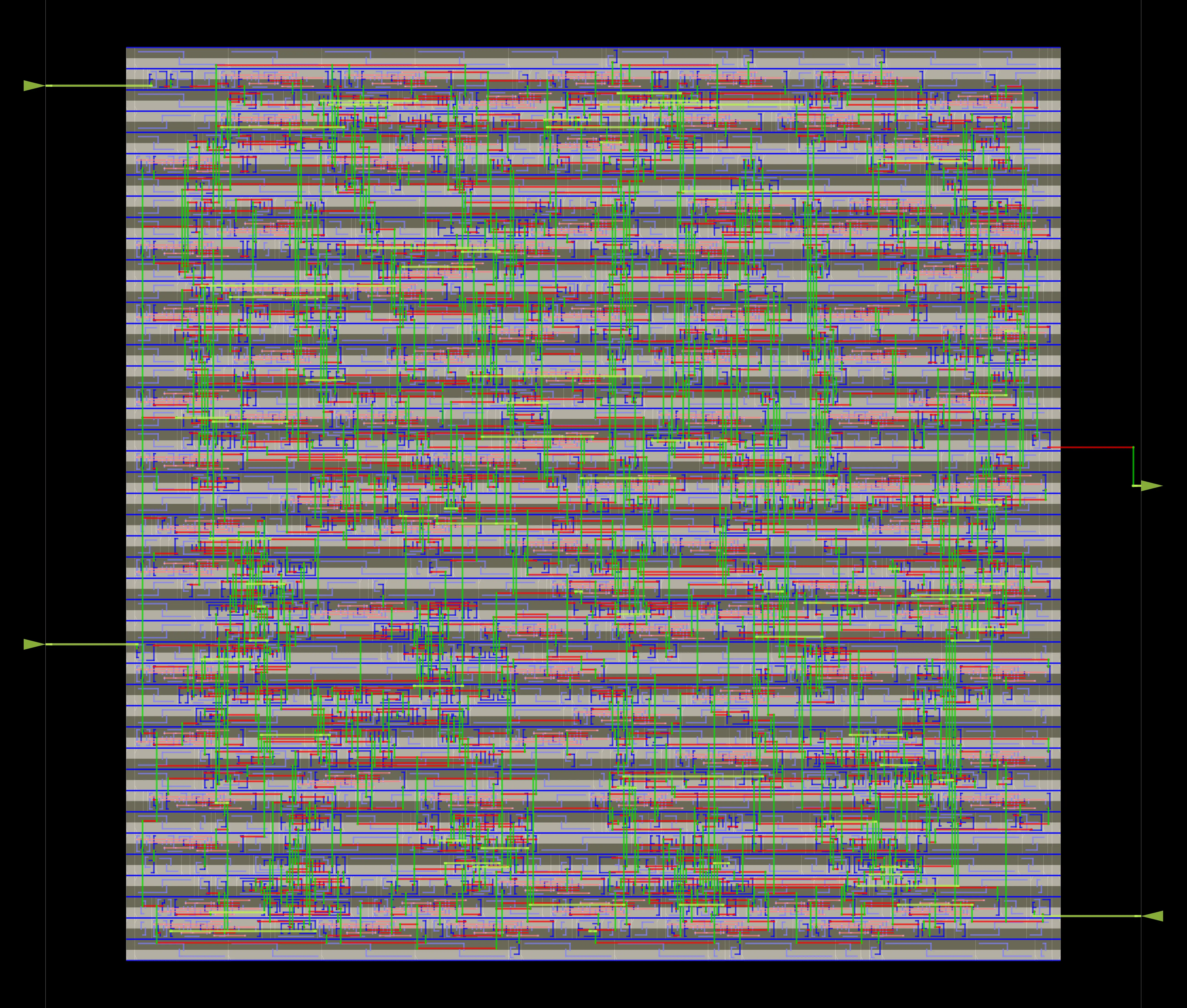

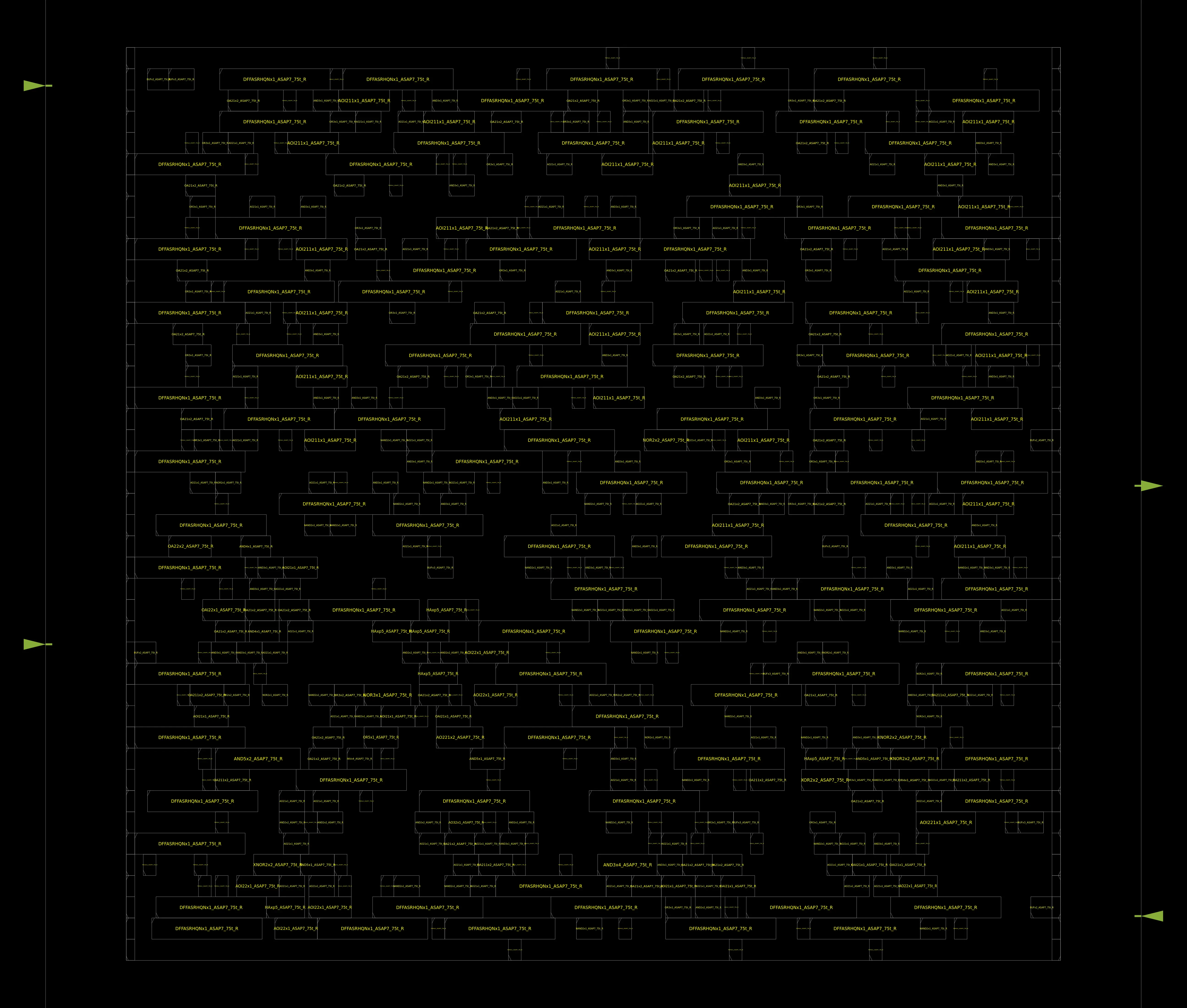

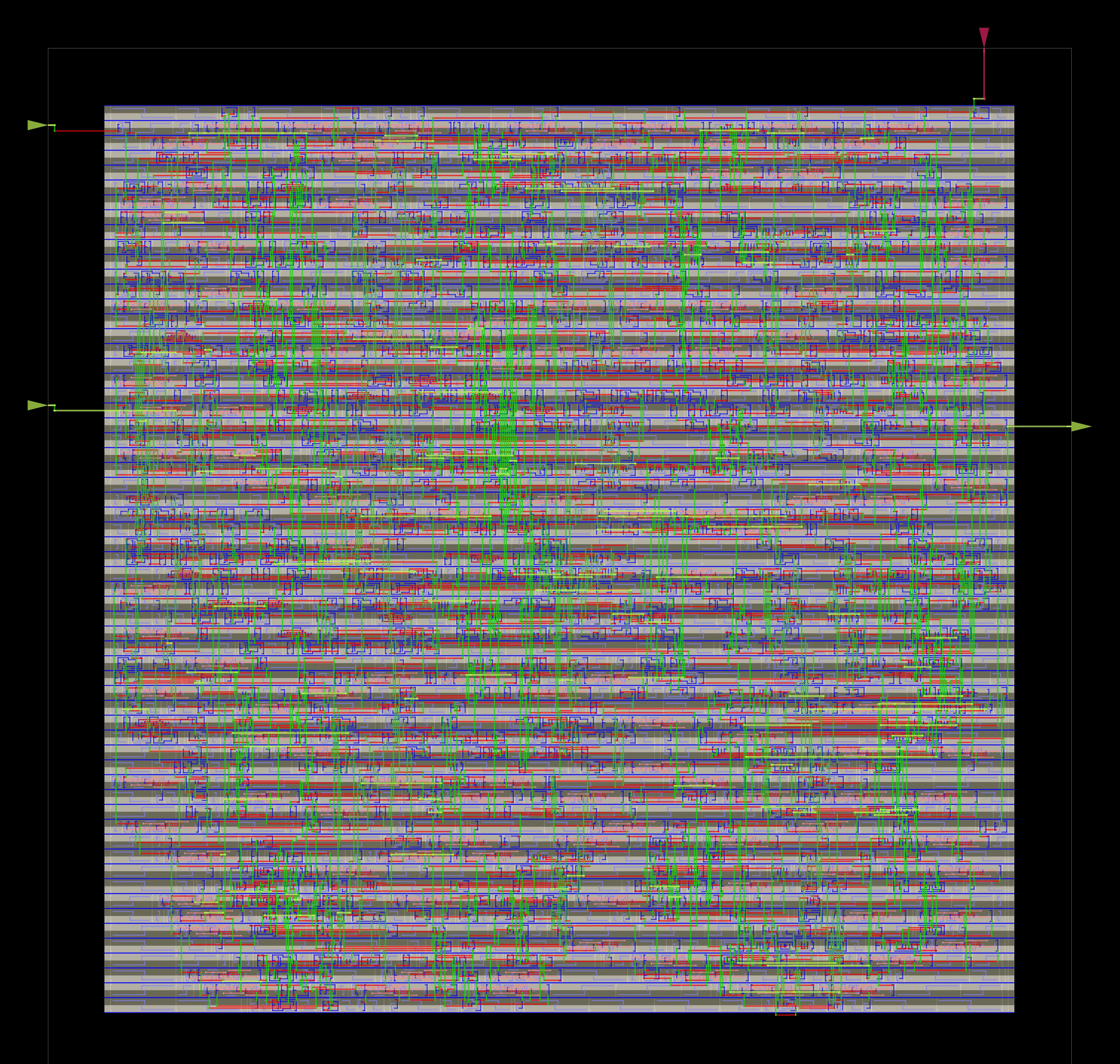

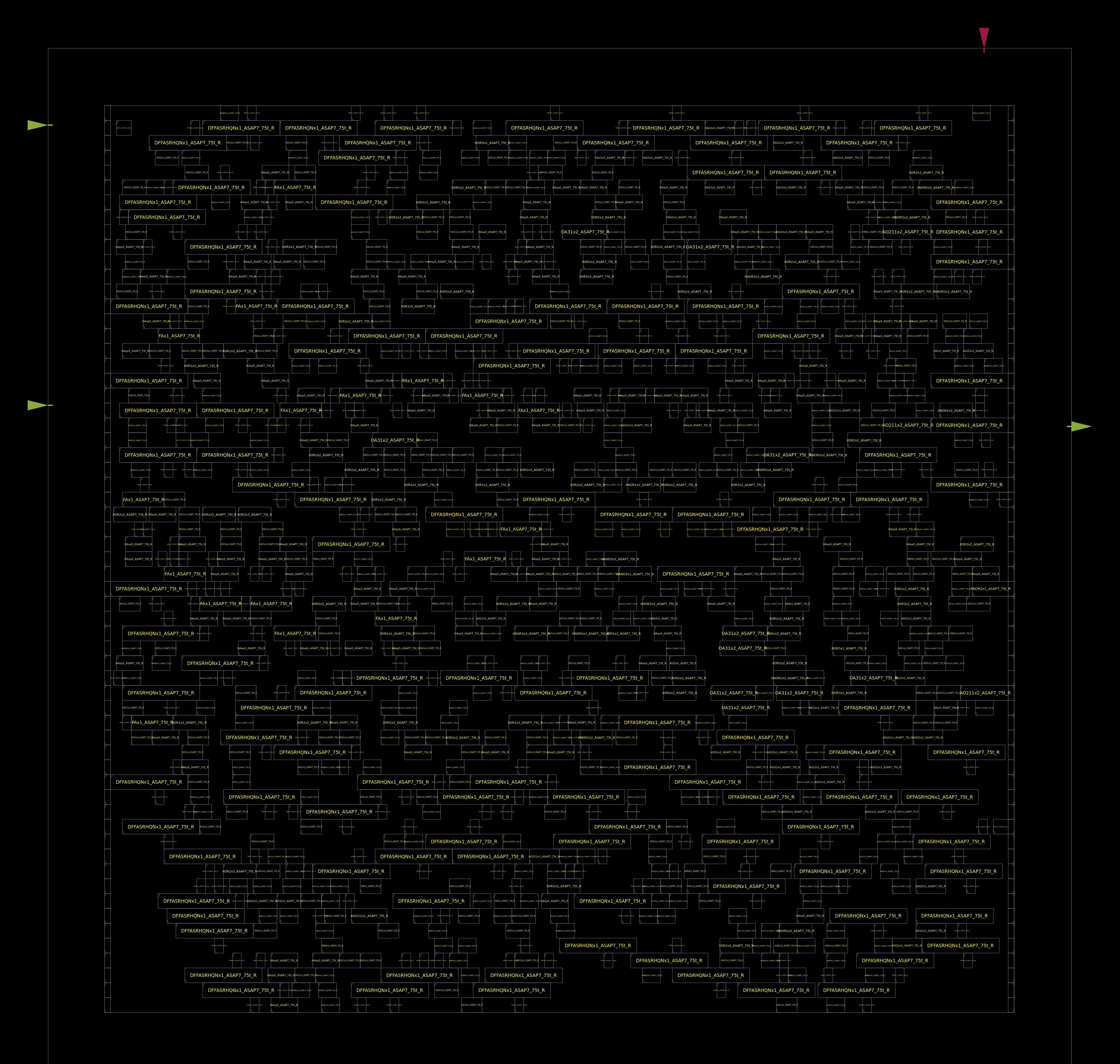

Waveforms and ASAP7 GDS¶

For each design our GitHub Actions flow runs

Simulation using Verilator, generating VCD, converted to SVG,

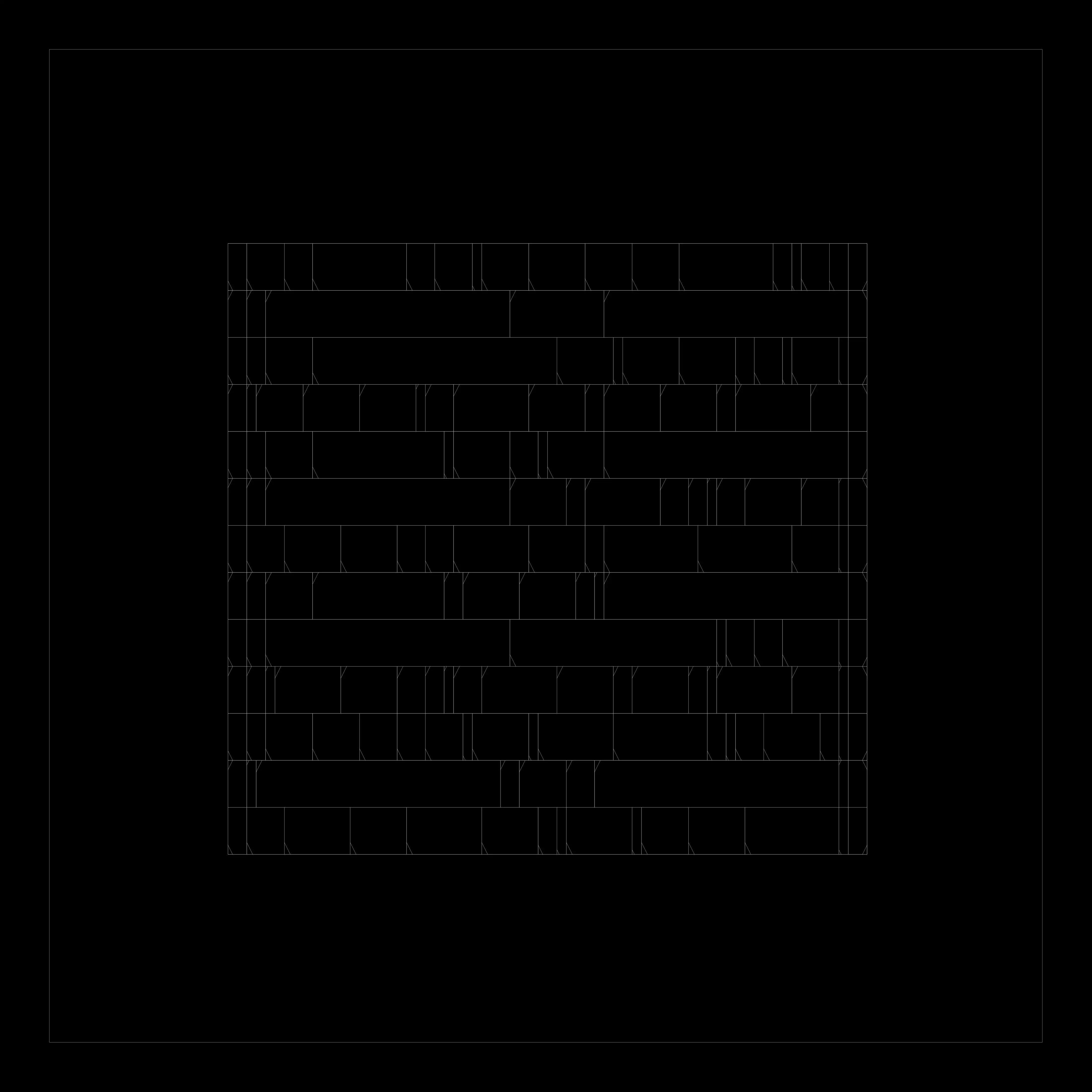

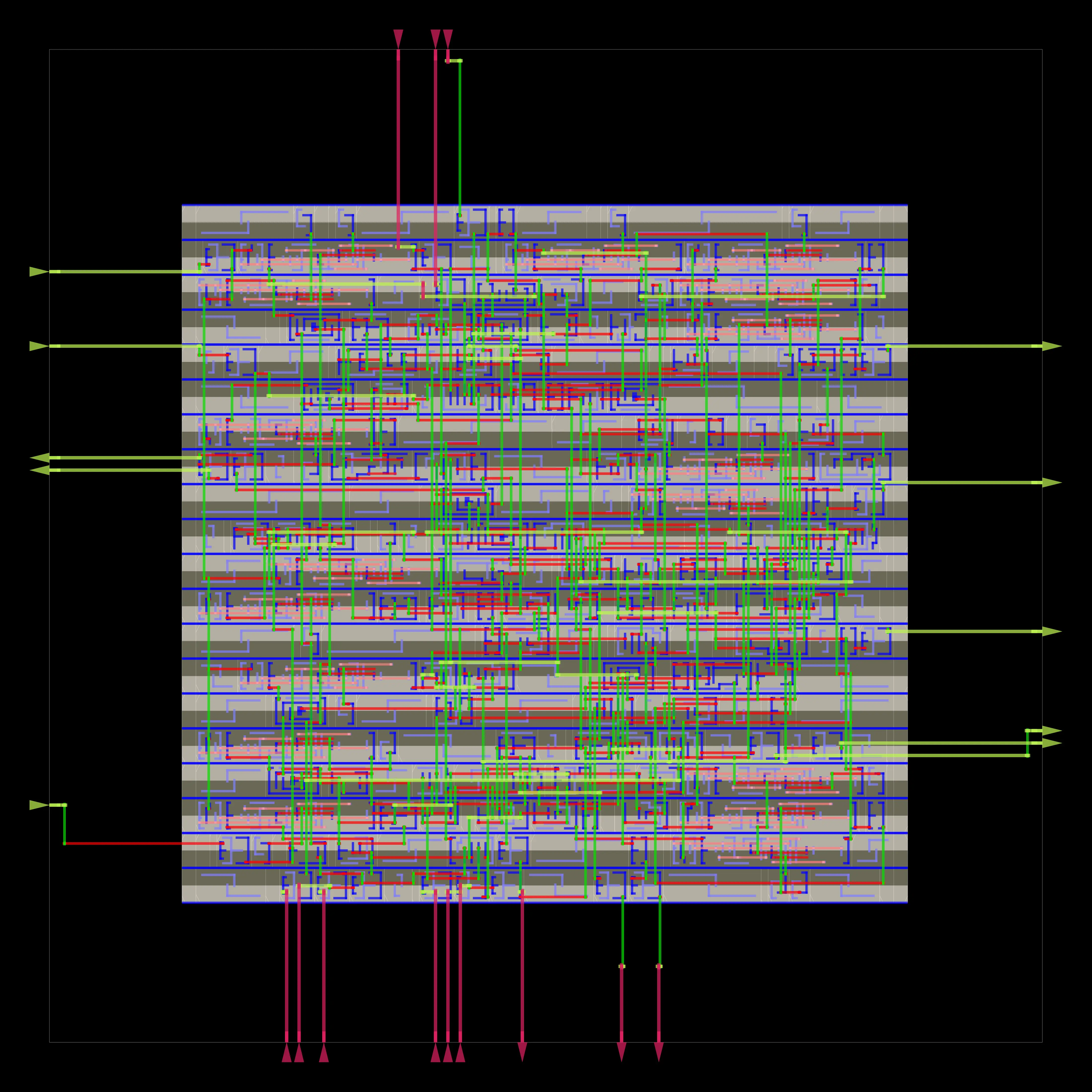

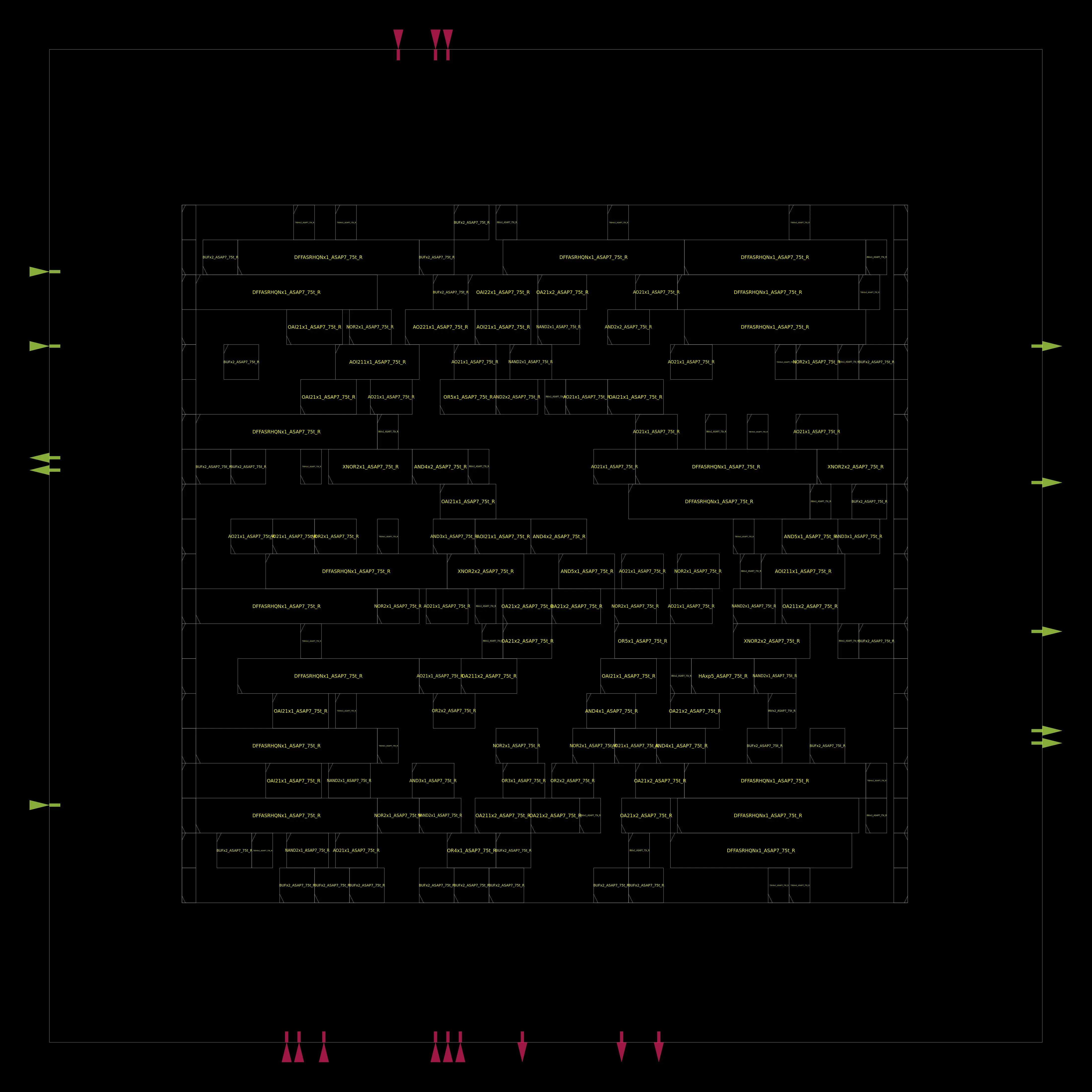

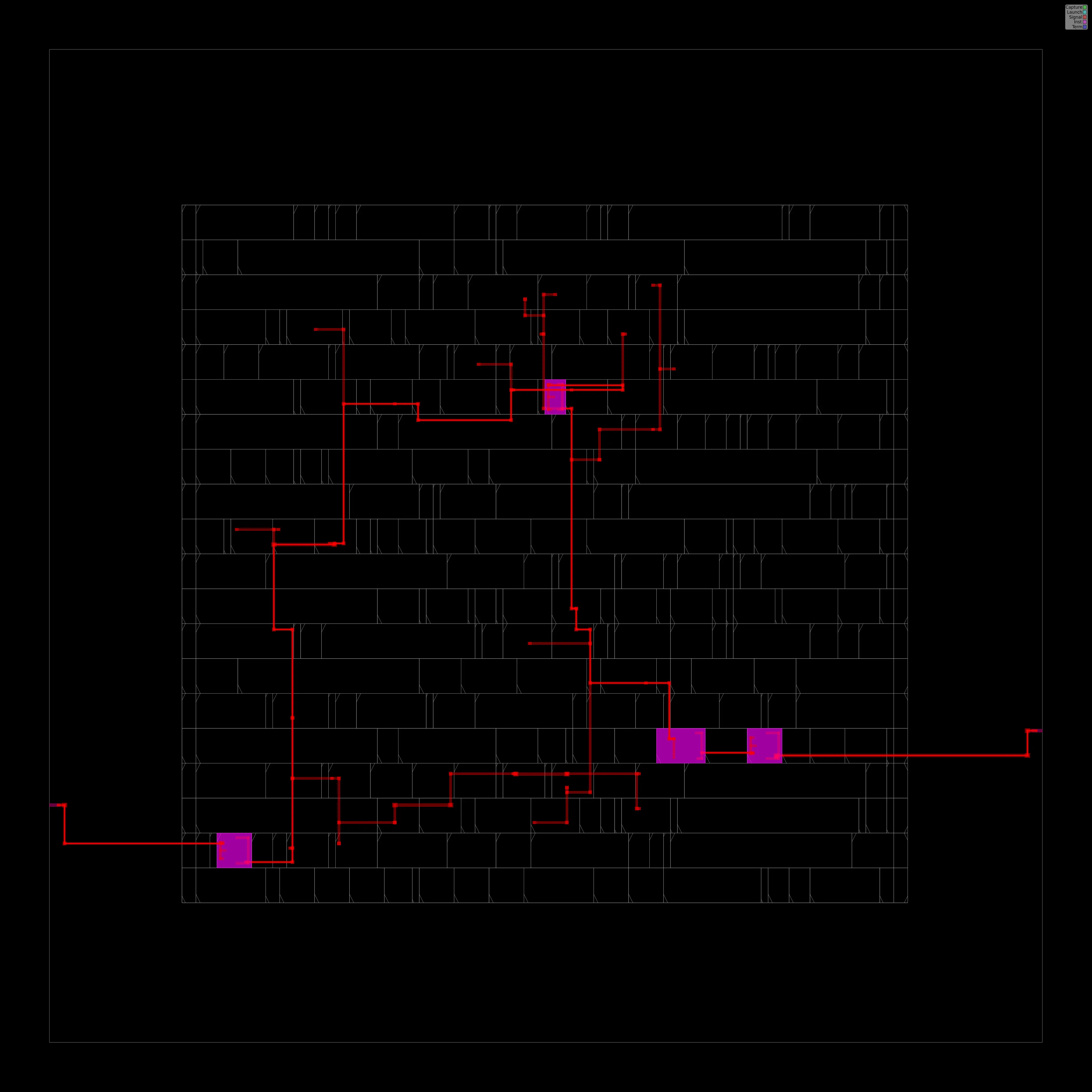

OpenROAD RTL2GDS2 flow using ASAP7 7nm, a realistic PDK for academic use,

collects their outputs and displays them here.

To reproduce this on your machine, check out our docker setup.

Our repository: github.com/abarajithan11/digital-design

Filelists: material/designs

SystemVerilog RTL: material/rtl

Testbenches: material/tb

Makefile: material/Makefile

OpenRoad Flow: material/openroad

1. Not Gate¶

Run results

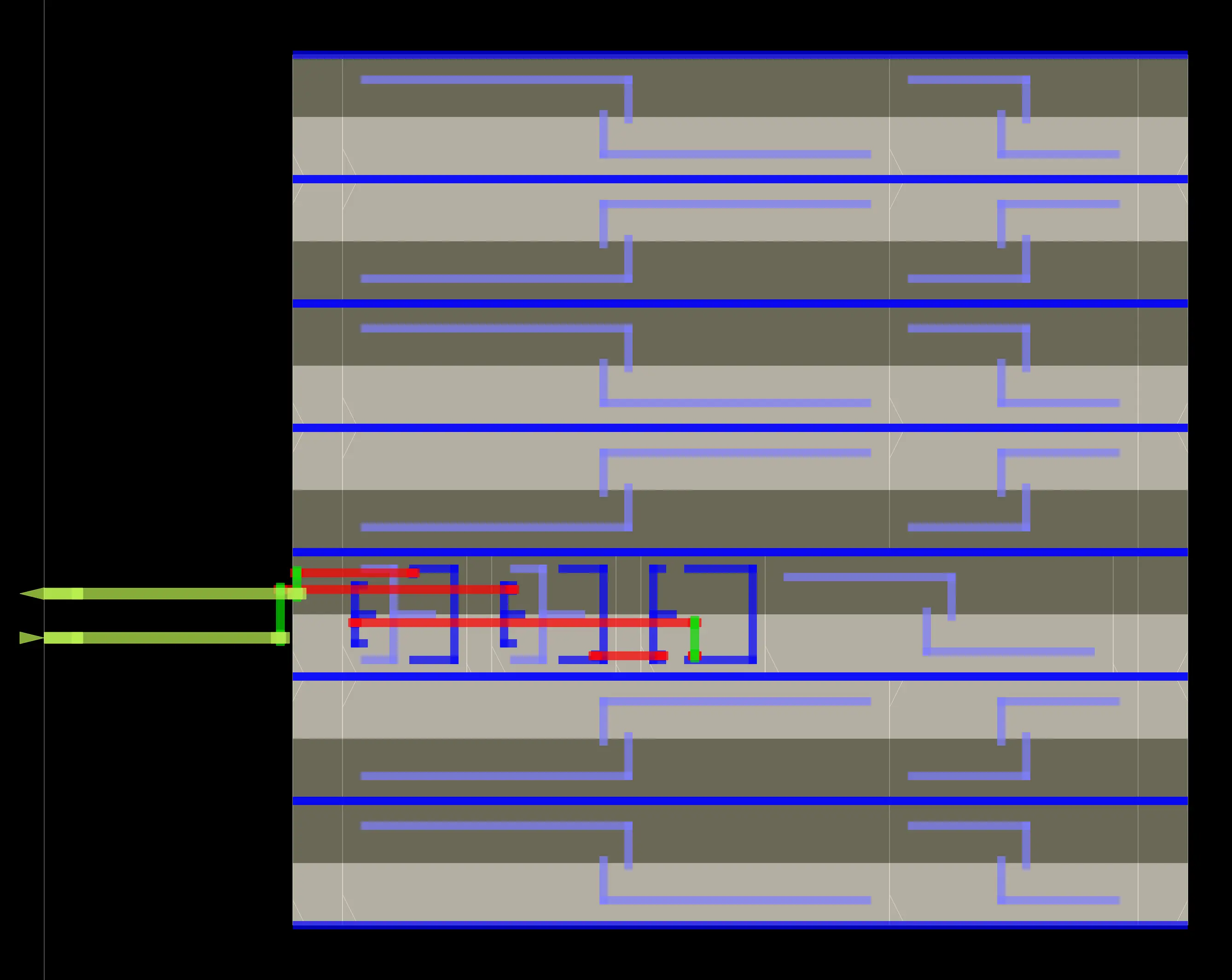

Waveform (0-10 ns)

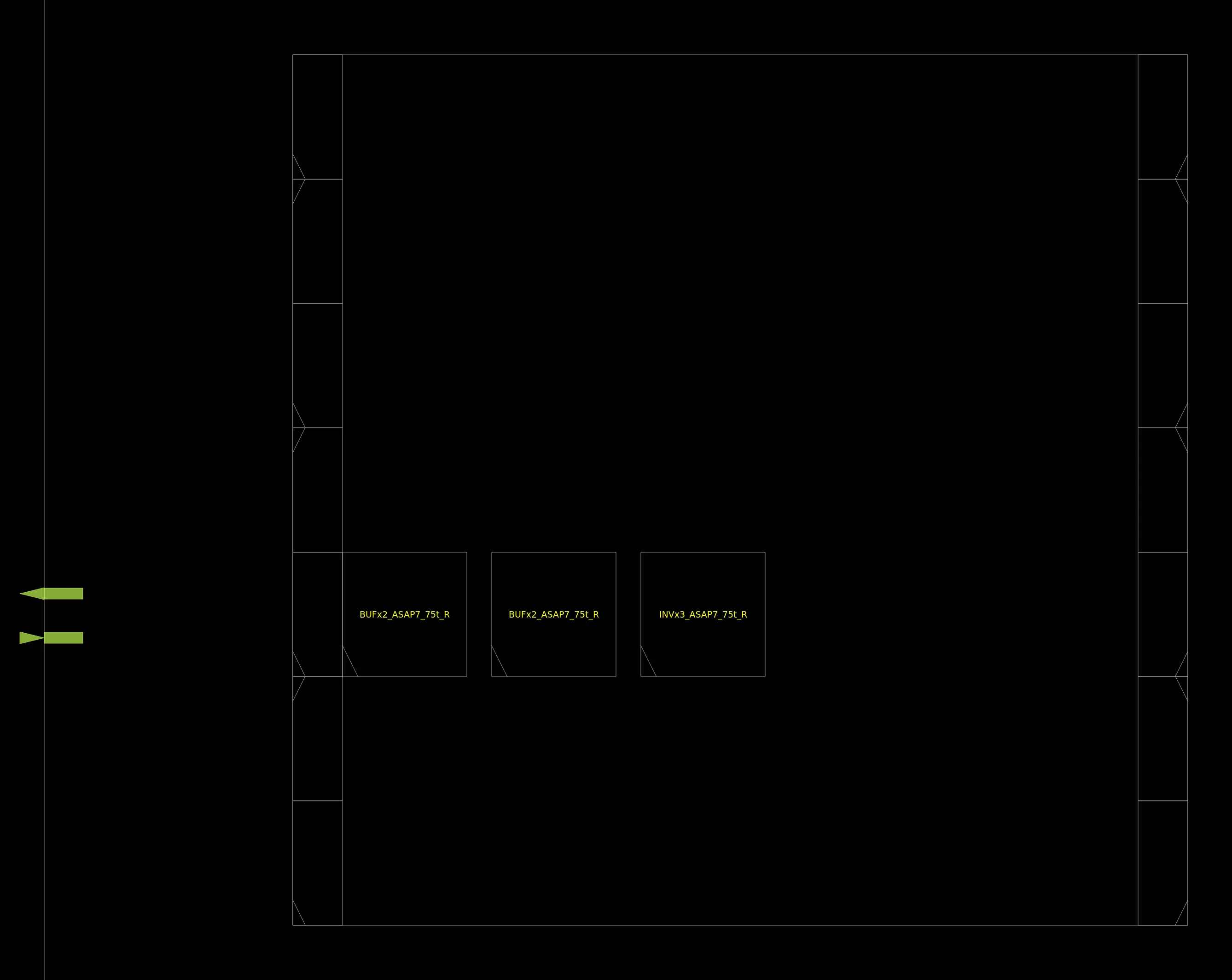

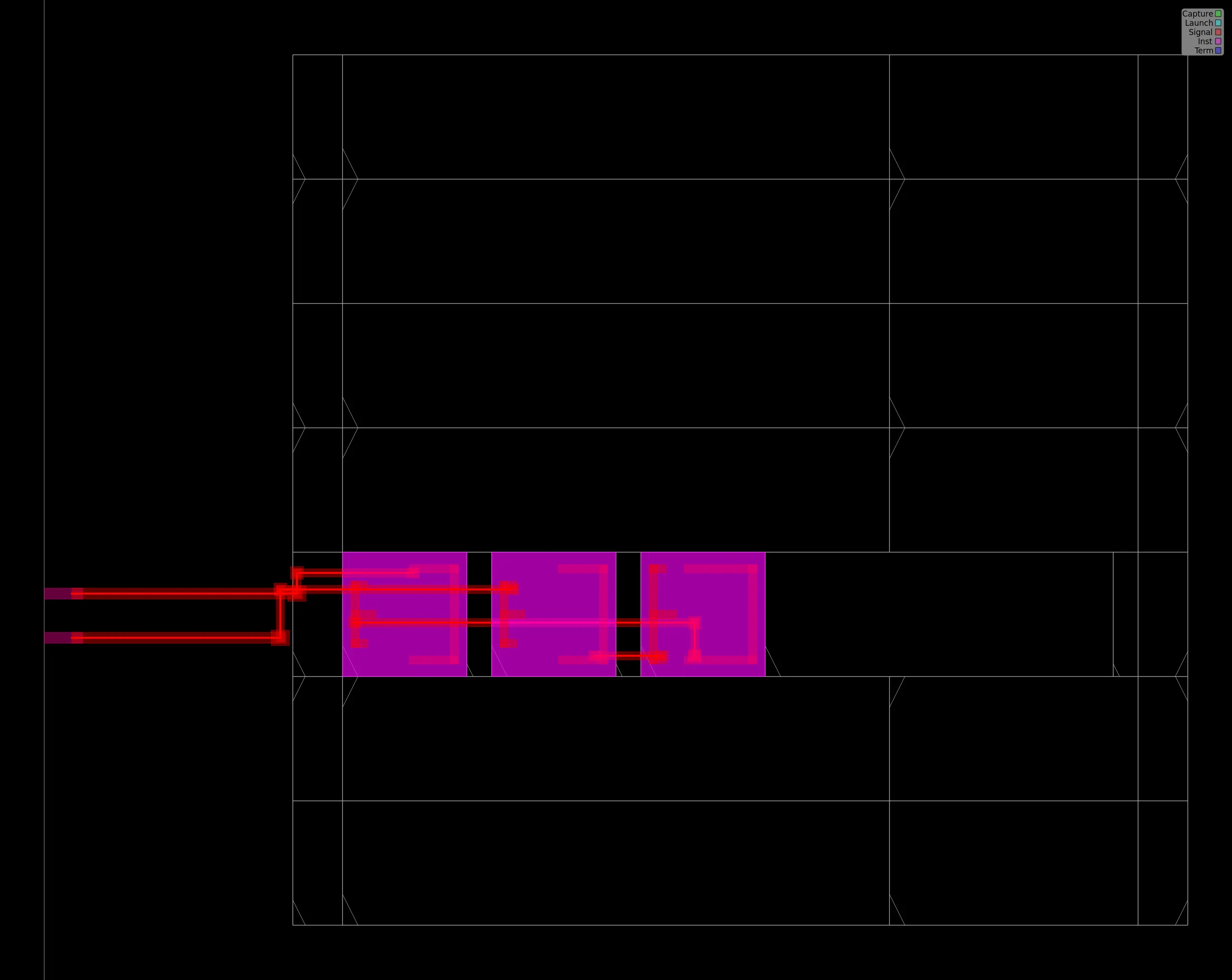

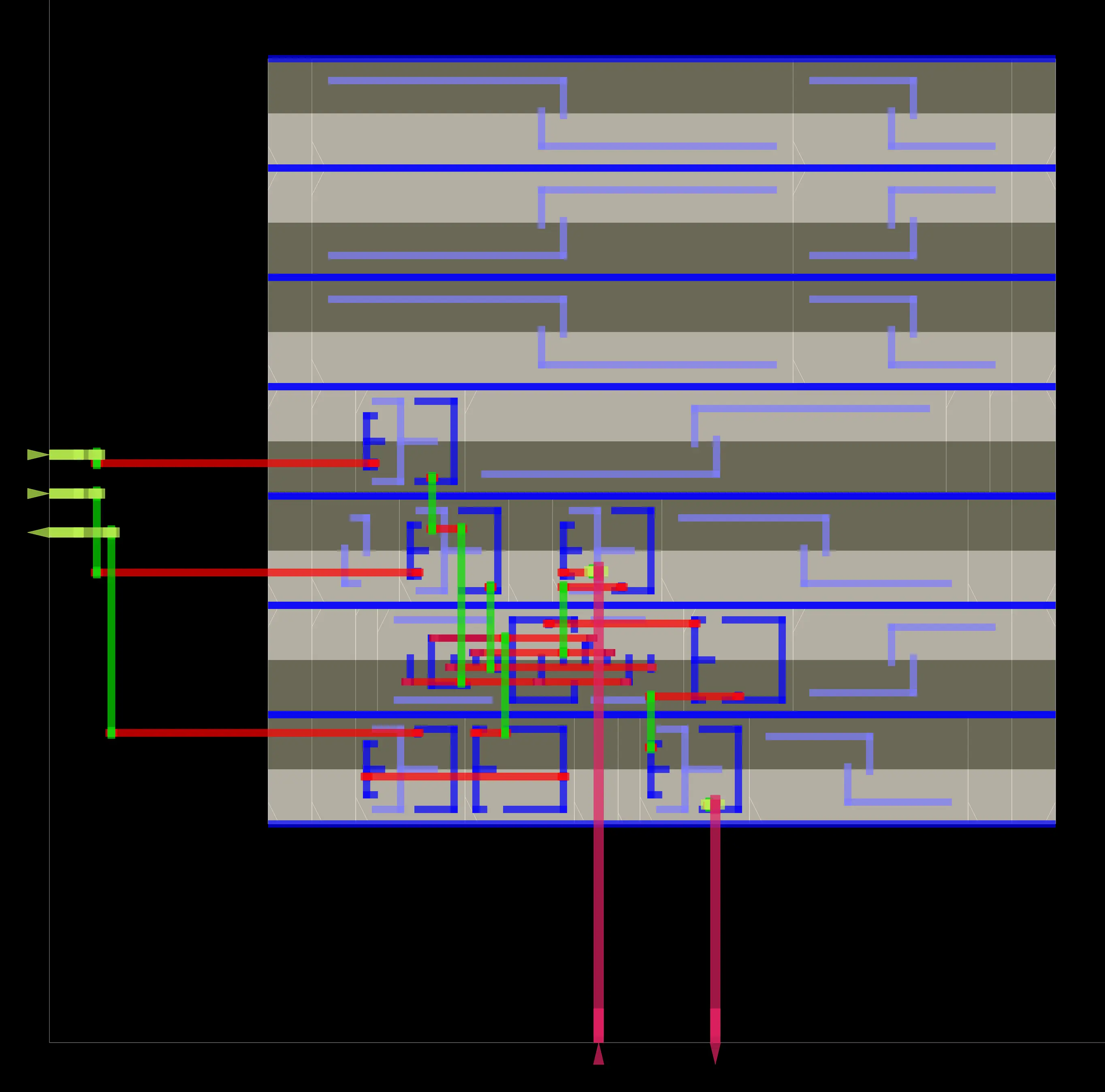

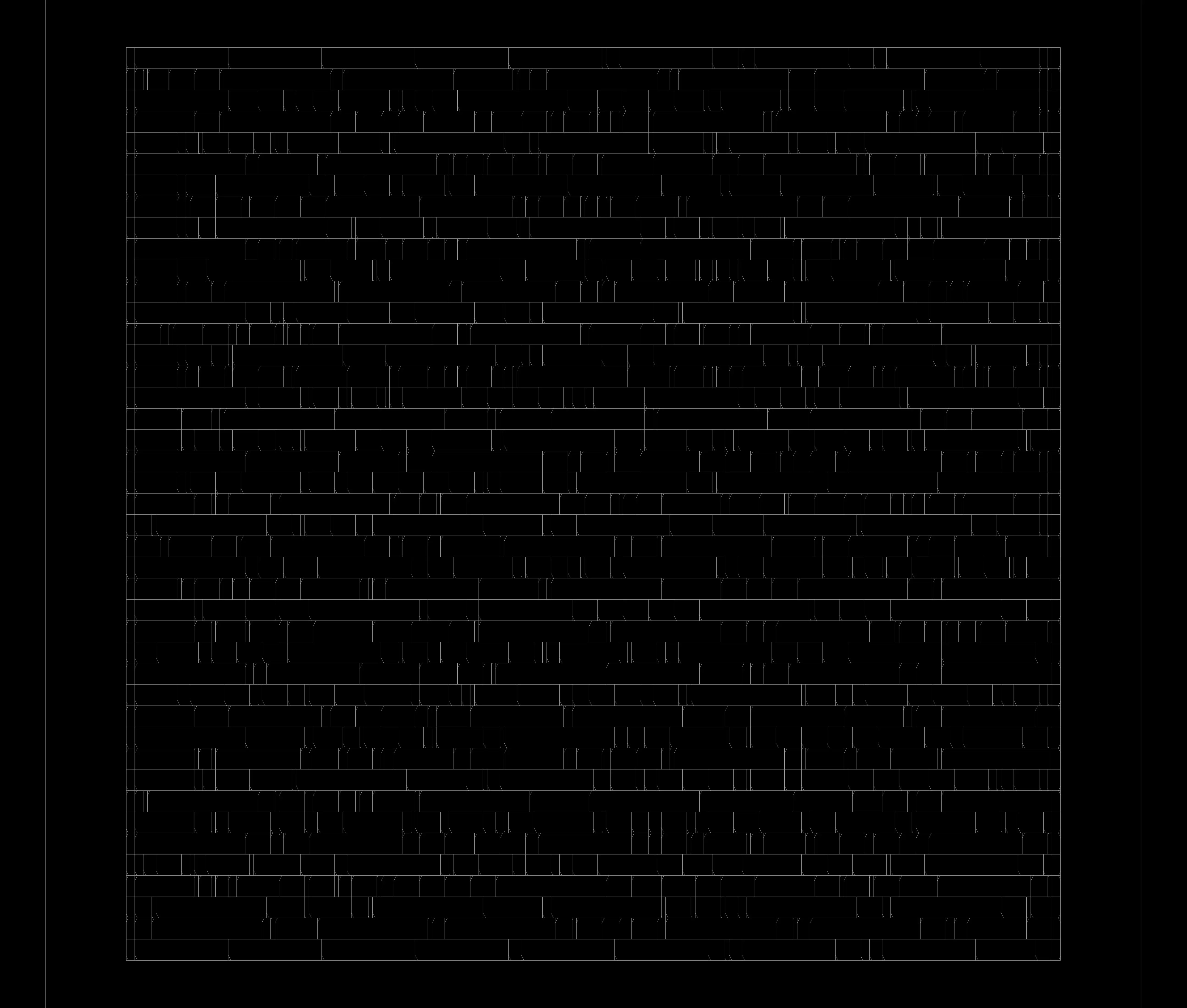

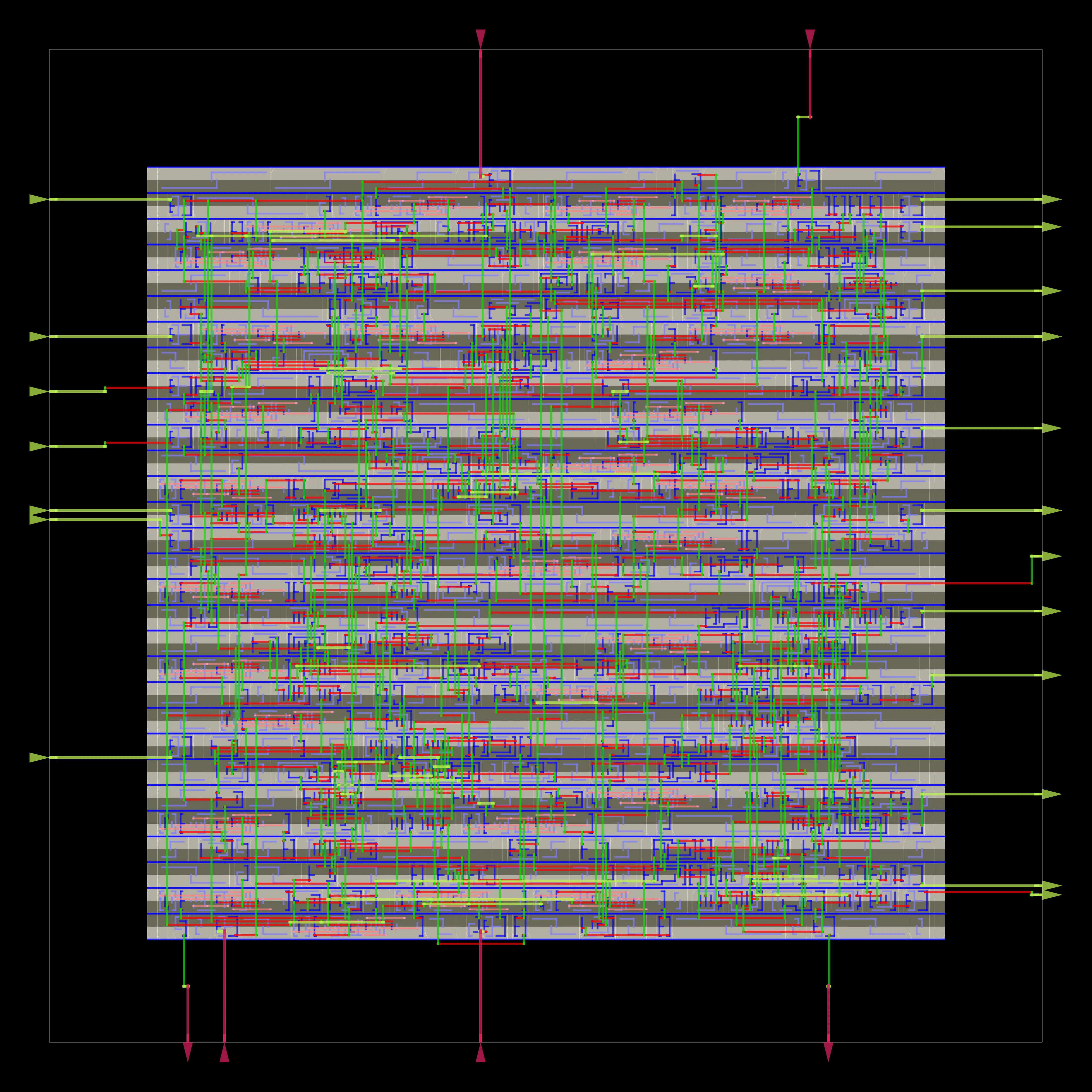

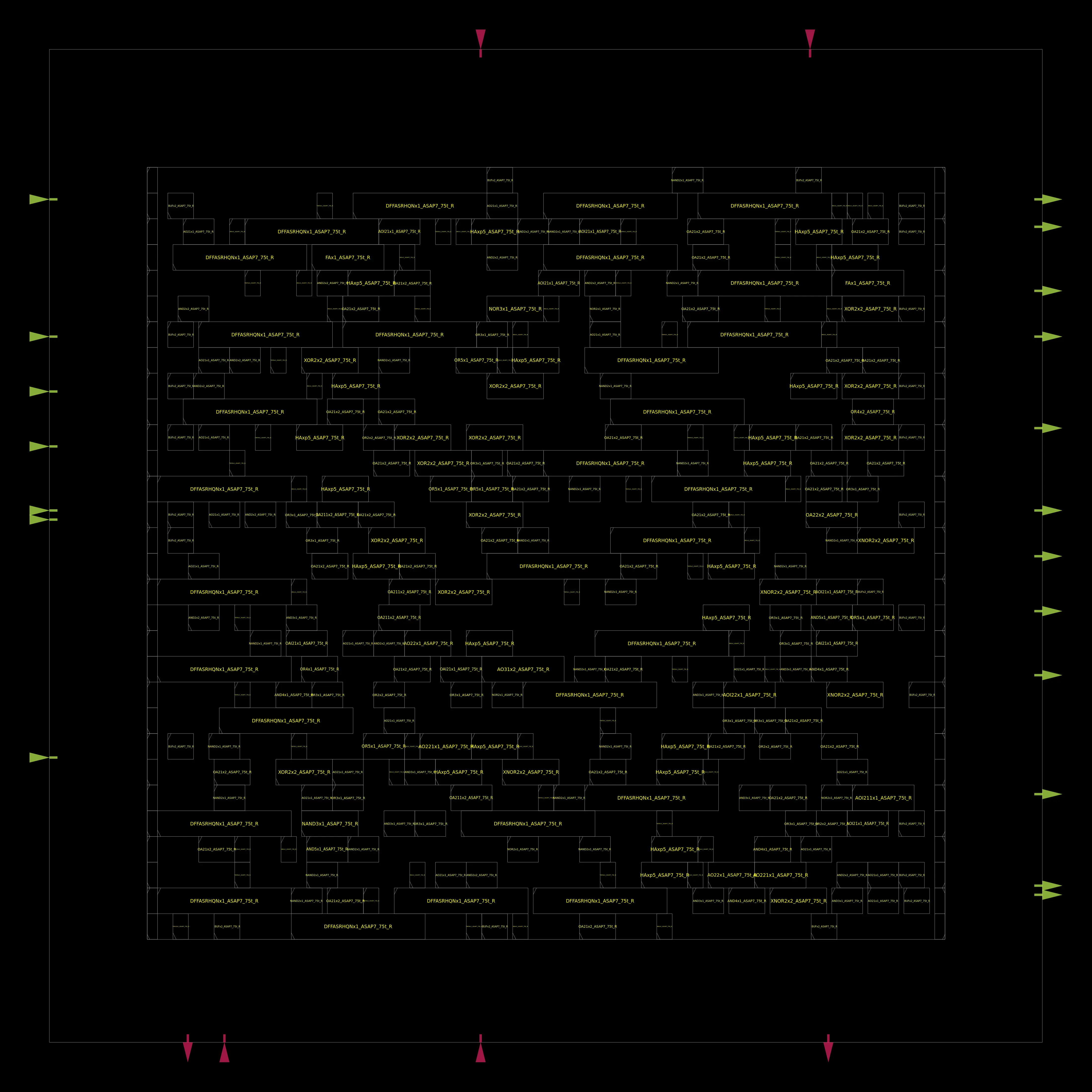

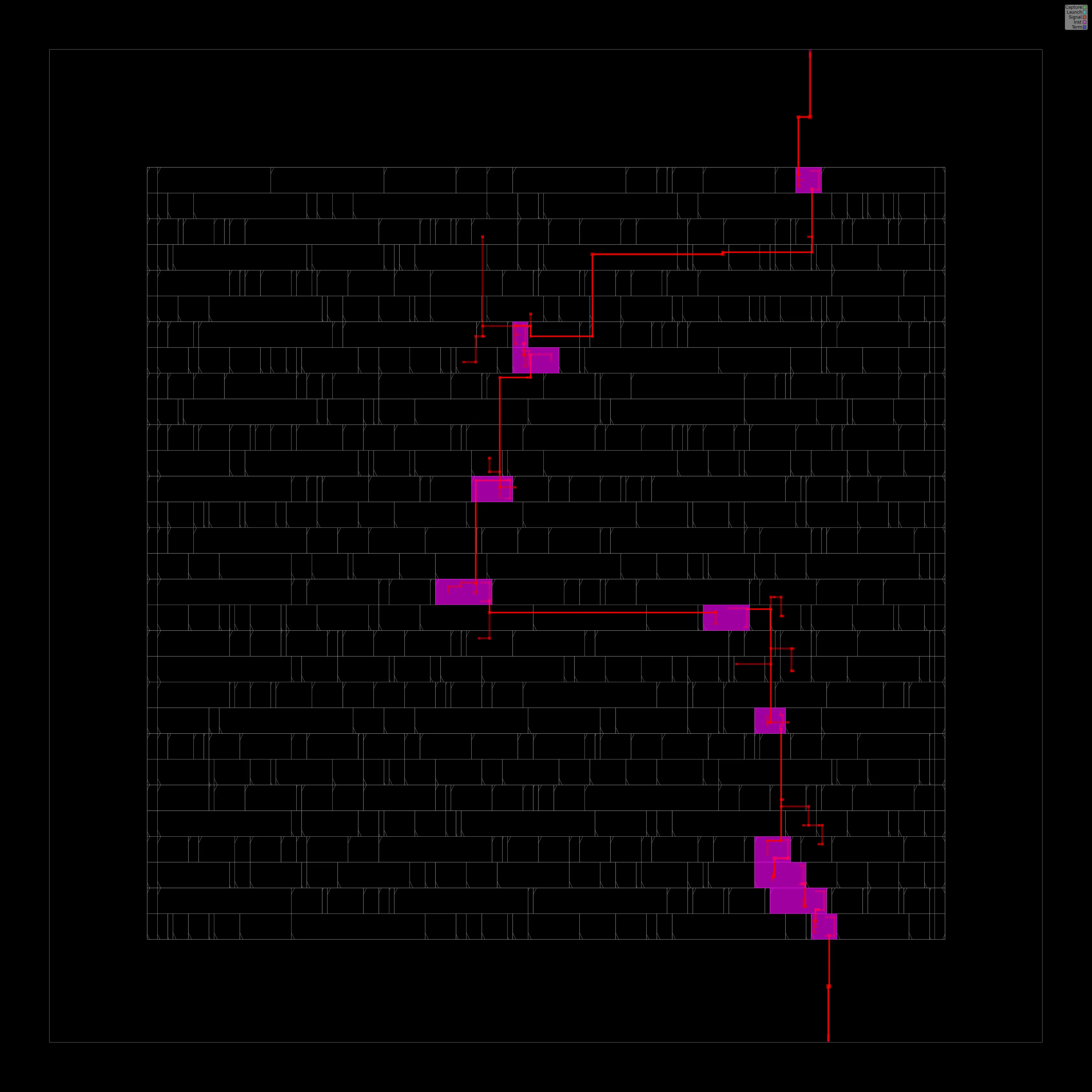

Layout Reports

Routing, Placement, Worst path

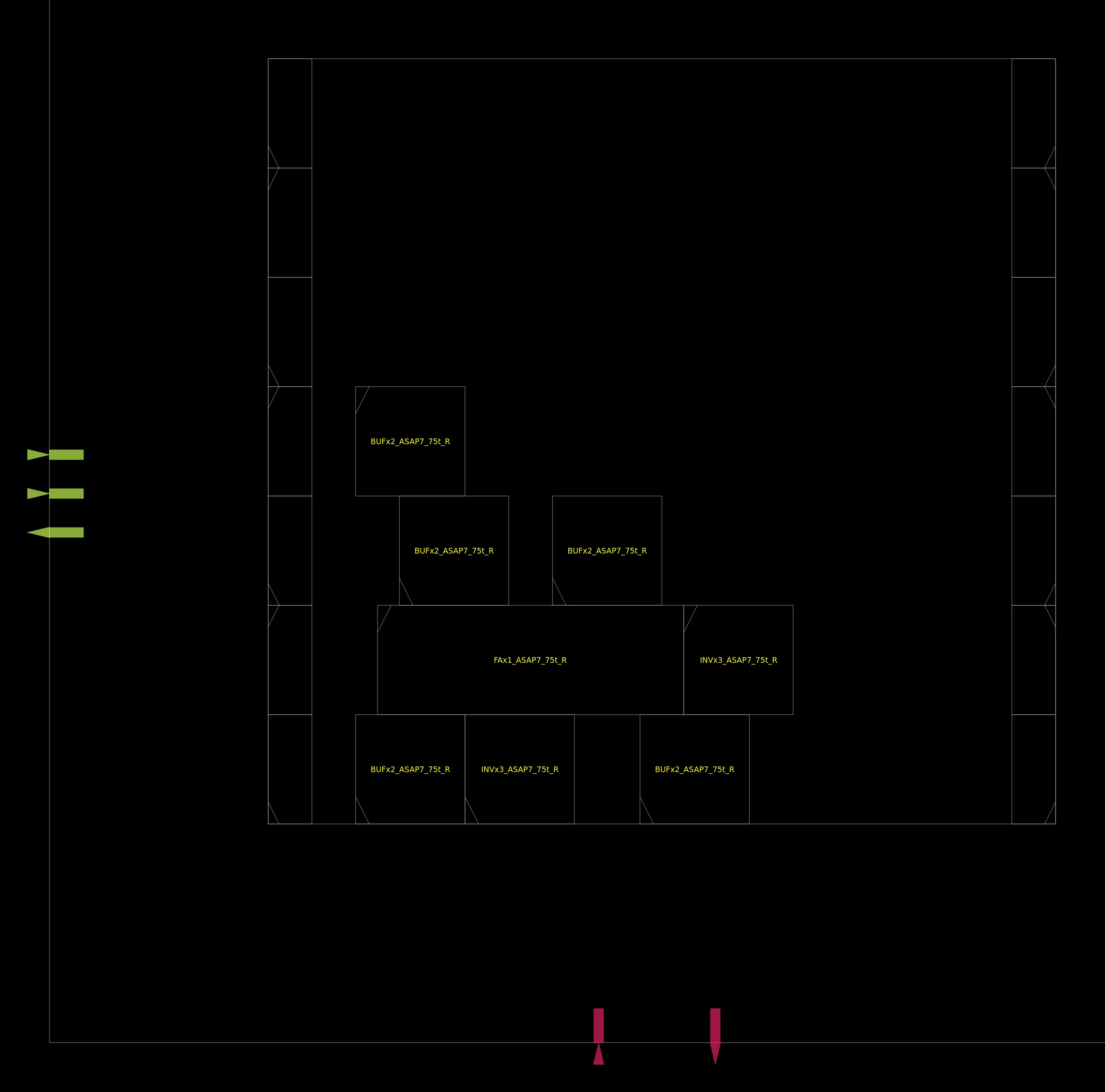

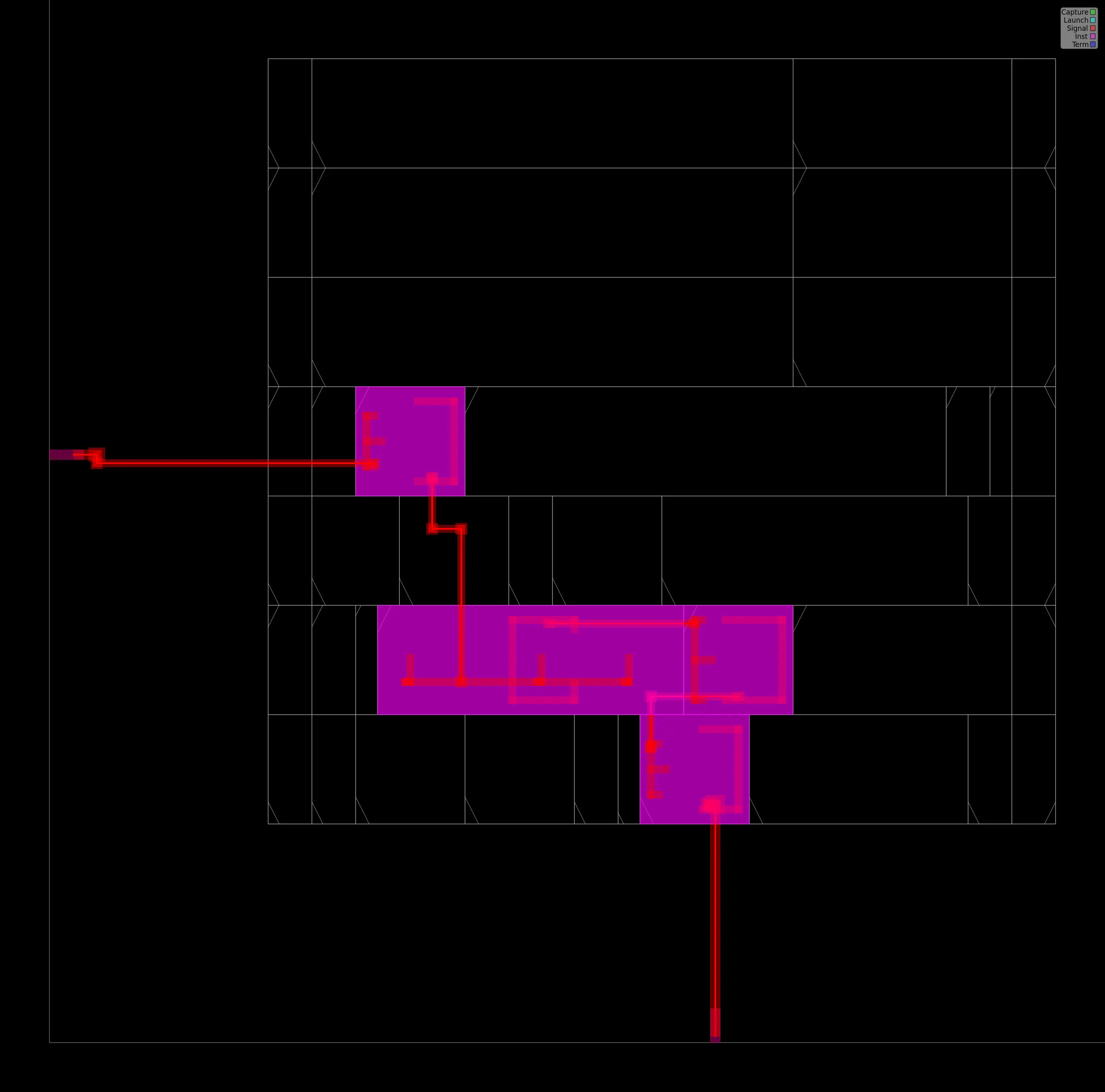

2. Full Adder¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

3. N Adder¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

4. Alu¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

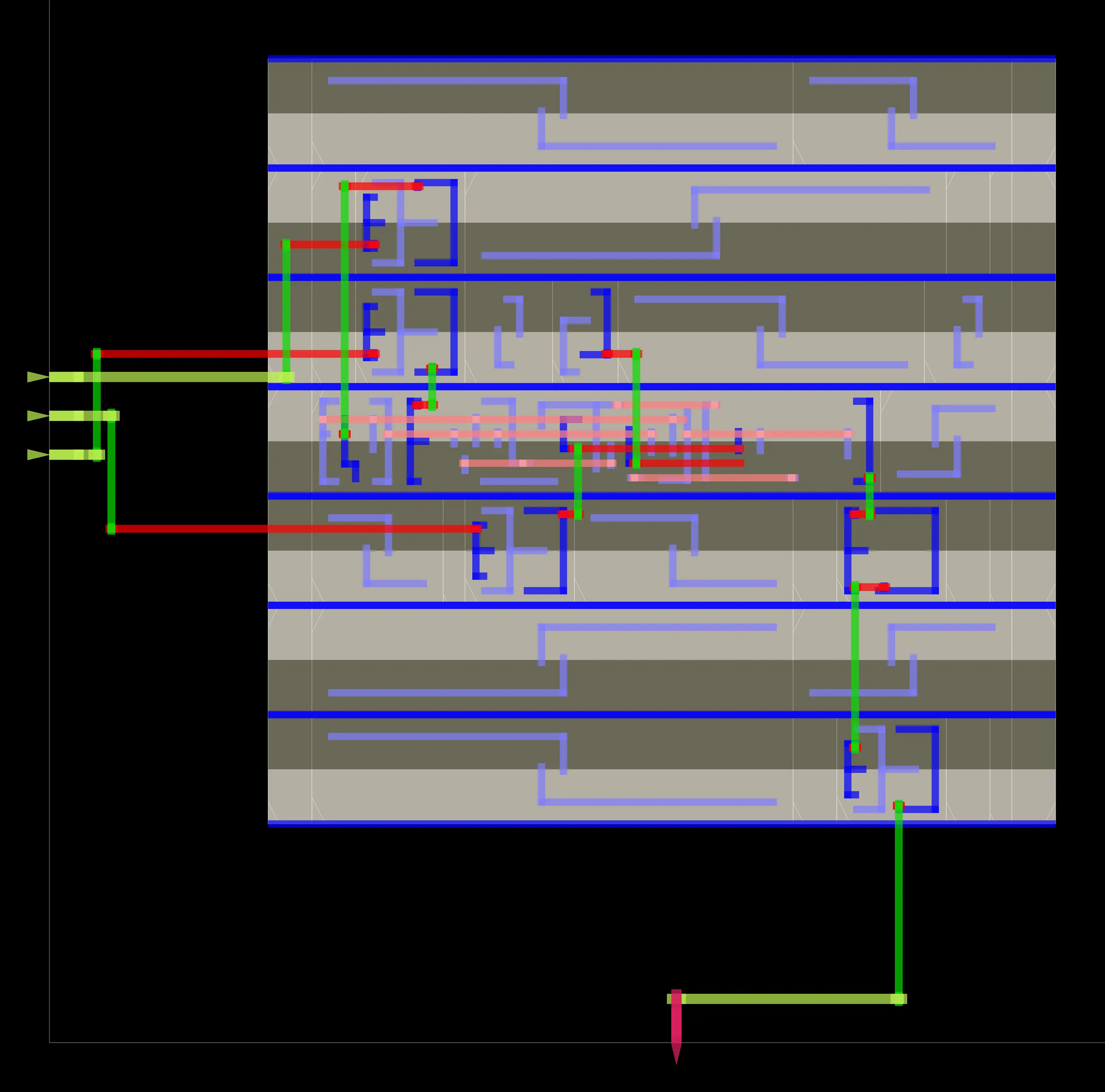

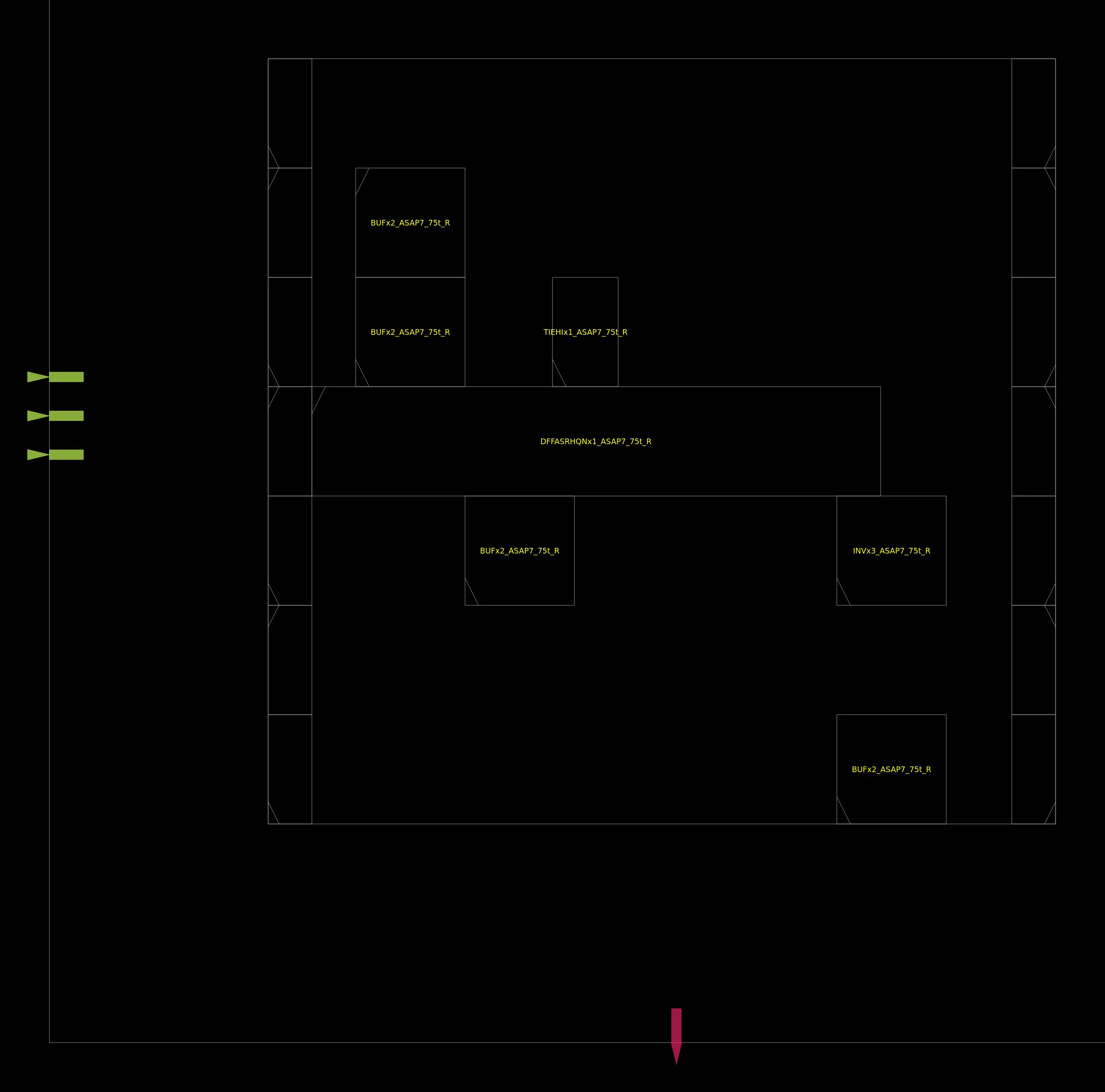

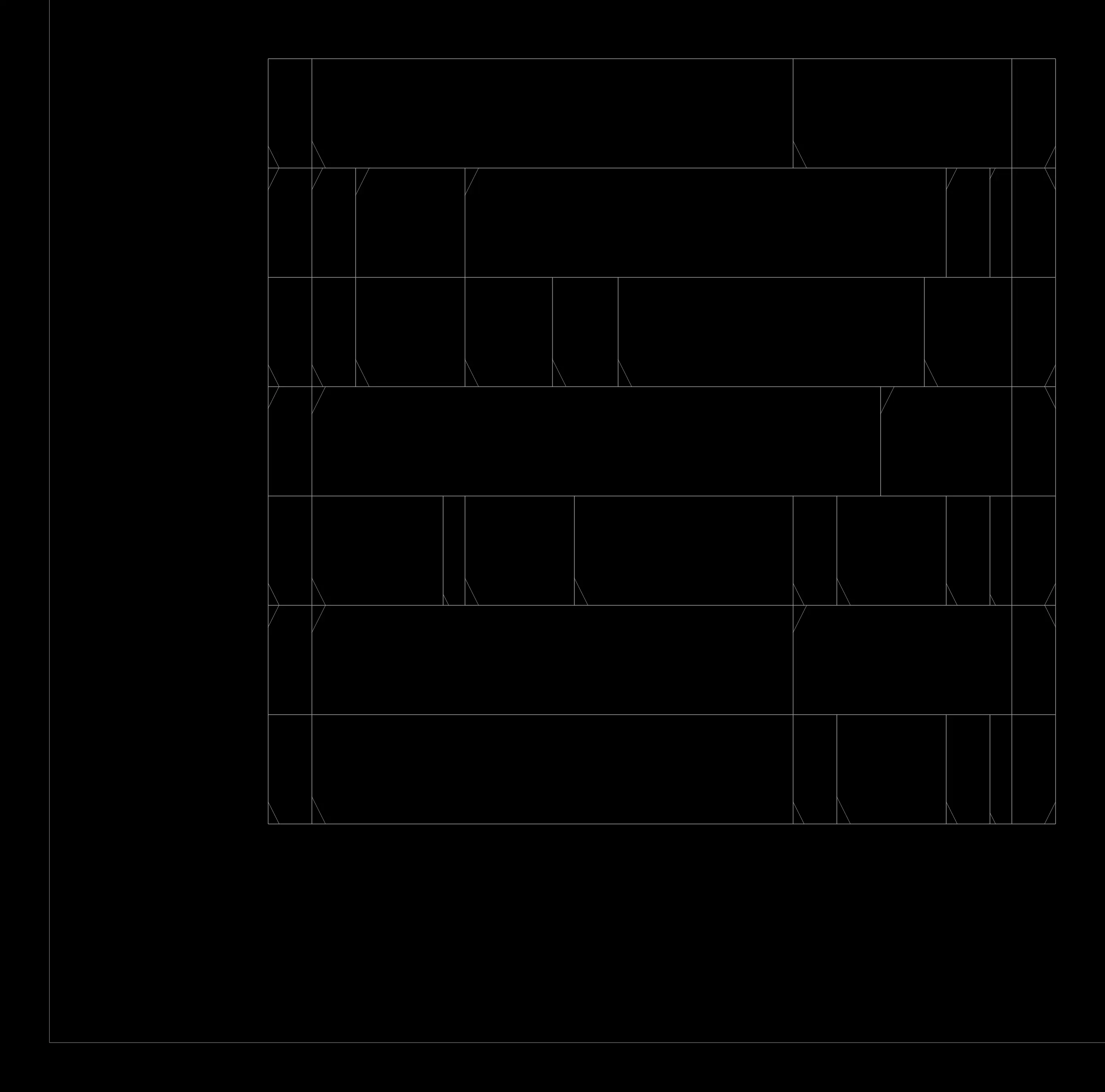

8. Flip Flop¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

9. Up Counter¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

11. Parallel To Serial¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

12. Down Counter¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

13. Uart Rx¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

14. Uart Tx¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

15. Uart Echo¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

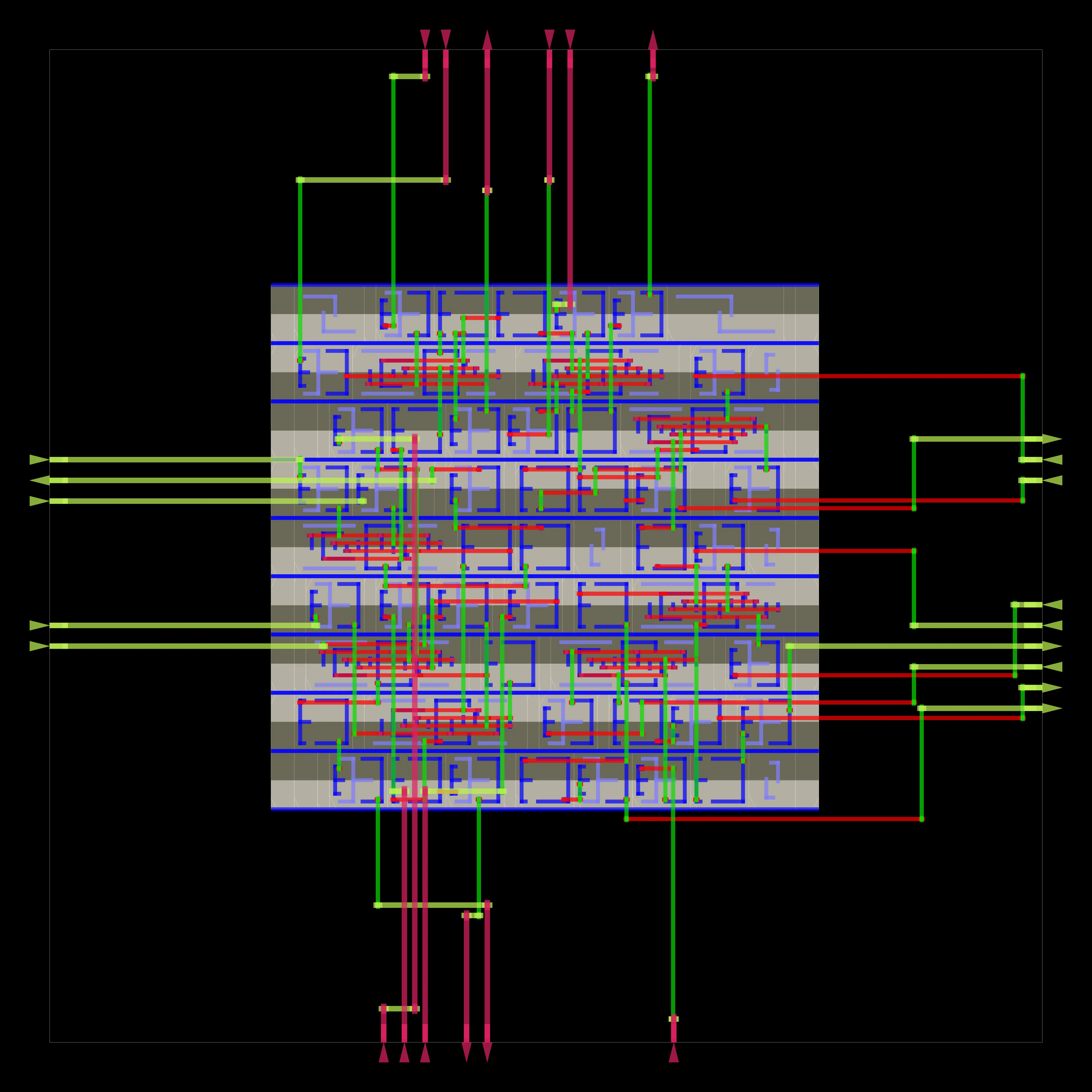

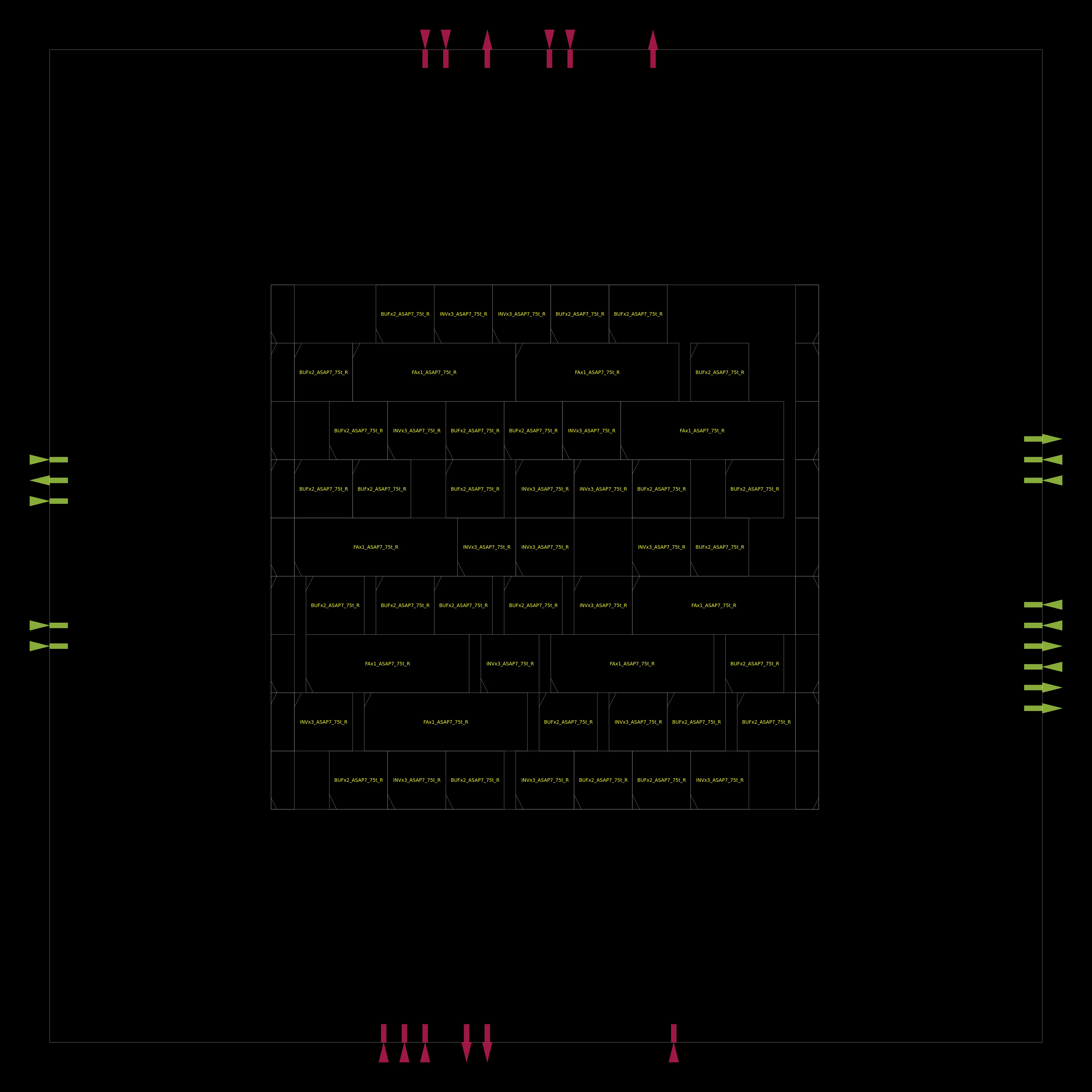

16. Fir Filter¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

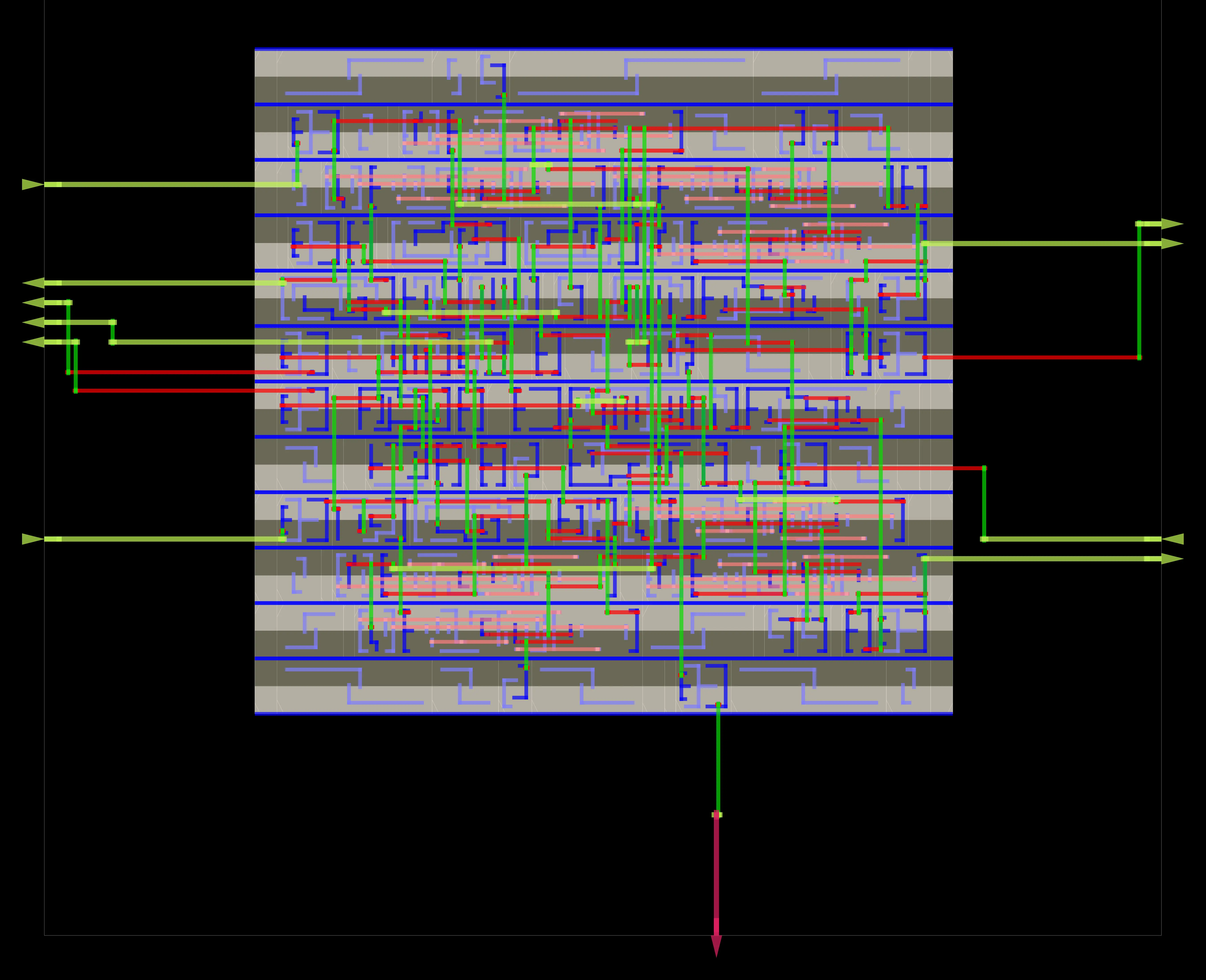

17. Sys Fir Filter¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path

18. Reduction Tree Min¶

Run results

Waveform (0-10 ns)

Layout Reports

Routing, Placement, Worst path